# Programmable 360° Inclinometer

ADIS16203

#### **FEATURES**

0° to 360° Inclinometer ±180 output format option 14-bit digital inclination outputs Linear output, 0.025° resolution 12-bit digital temperature sensor output Digitally controlled bias calibration Digitally controlled sample rate Digitally controlled filtering Digitally controlled direction/orientation Dual alarm settings with rate/threshold limits Auxiliary digital I/O Digitally activated self-test Digitally activated low power mode SPI®-compatible serial interface **Auxiliary 12-bit ADC input and DAC output** Single-supply operation: 3.0 V to 3.6 V 3500 g powered shock survivability

#### **APPLICATIONS**

Tilt sensing, inclinometers

Platform control, stabilization, and leveling

Motion/position measurement

Monitor/alarm devices (security, medical, safety)

Robotics

#### **GENERAL DESCRIPTION**

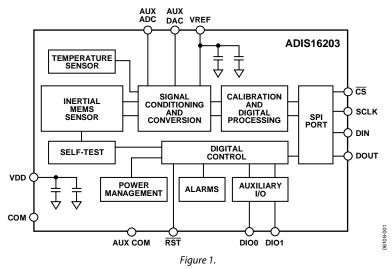

The ADIS16203 is a complete incline-angle measurement system in a single compact package enabled by the Analog Devices, Inc., *i*Sensor™ integration. By enhancing the Analog Devices *i*MEMS® sensor technology with an embedded signal processing solution, the ADIS16203 provides factory-calibrated, sensor-to-digital incline-

angle data in a convenient format that can be accessed using a serial peripheral interface (SPI). The SPI interface provides access to multiple measurements: 360° linear inclination angles, ±180° linear incline angles, temperature, power supply, and one auxiliary analog input. Easy access to calibrated digital sensor data provides developers with a system-ready device, reducing development time, cost, and program risk.

Unique characteristics of the end system are accommodated easily through several built-in features, such as a single-command offset calibration, along with convenient sample rate and bandwidth control.

The ADIS16203 offers the following embedded features that eliminate the need for external circuitry and provide a simplified system interface:

- Configurable alarm function

- Auxiliary 12-bit analog-to-digital converter (ADC)

- Auxiliary 12-bit digital-to-analog converter (DAC)

- Configurable digital I/O port

- Digital self-test function

The ADIS16203 offers two power management features for managing system-level power dissipation: low power mode and a configurable shutdown feature.

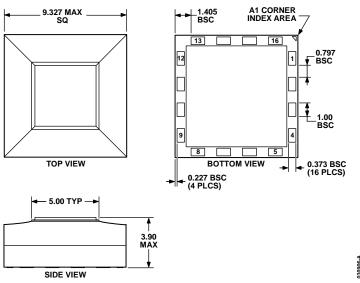

The ADIS16203 is available in a 9.2 mm  $\times$  9.2 mm  $\times$  3.9 mm laminate-based land grid array (LGA) package with a temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

#### **FUNCTIONAL BLOCK DIAGRAM**

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

## **TABLE OF CONTENTS**

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| General Description1                         |

| Functional Block Diagram 1                   |

| Revision History                             |

| Specifications                               |

| Timing Specifications5                       |

| Timing Diagrams5                             |

| Absolute Maximum Ratings6                    |

| ESD Caution6                                 |

| Pin Configuration and Function Descriptions7 |

| Typical Performace Characteristics           |

| Theory of Operation11                        |

| Output Response11                            |

| Temperature Sensor                           |

| Basic Operation                              |

| Serial Peripheral Interface (SPI)12          |

| Data Output Register Access                  |

| Programming and Control14                    |

| Control Register Overview14                  |

| Control Register Access                      |

| Control Register Details15                   |

| Calibration                                  |

|    | Calibration Register Definition            | 15 |

|----|--------------------------------------------|----|

|    | Alarms                                     | 15 |

|    | Sample Period Control                      | 18 |

|    | Filtering Control                          | 18 |

|    | Power-Down Control                         | 19 |

|    | Status Feedback                            | 20 |

|    | COMMAND Control                            | 20 |

|    | Miscellaneous Control Register             | 21 |

| ο, | eripherals                                 | 22 |

|    | Auxiliary ADC Function                     | 22 |

|    | Auxiliary DAC Function                     | 22 |

|    | General-Purpose I/O Control                | 23 |

| 4  | pplications                                | 24 |

|    | Hardware Considerations                    | 24 |

|    | Grounding and Board Layout Recommendations | 24 |

|    | Self-Test Tips                             | 24 |

|    | Band Gap Reference                         | 24 |

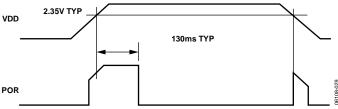

|    | Power-On Reset Operation                   | 25 |

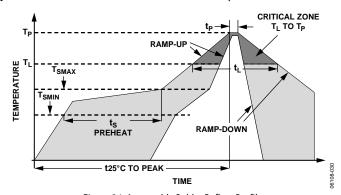

|    | Second-Level Assembly                      | 25 |

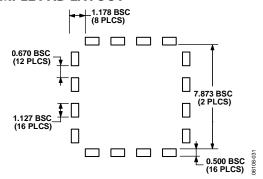

|    | Example Pad Layout                         | 25 |

| C  | outline Dimensions                         | 26 |

|    | Ordering Guide                             | 26 |

### **REVISION HISTORY**

8/06—Revision 0: Initial Version

# **SPECIFICATIONS**

$T_A = -40$  °C to +125 °C, VDD = 3.3 V, tilt = 0°, unless otherwise noted.

Table 1.

| Parameter                                                | Conditions                   | Min | Тур       | Max         | Unit        |

|----------------------------------------------------------|------------------------------|-----|-----------|-------------|-------------|

| INCLINOMETER <sup>1</sup>                                |                              |     | •         |             |             |

| Input Range                                              |                              |     | 360       |             | Degrees     |

| Relative Accuracy                                        | 25°C, maximum filter setting |     | ±0.6      |             | Degrees     |

| Sensitivity                                              | 25°C                         |     | 0.025     |             | Degrees/LSB |

| Accuracy Temperature Coefficient                         |                              |     | ±0.0167   |             | Degrees/°C  |

| NOISE PERFORMANCE                                        |                              |     |           |             |             |

| Output Noise                                             | At 25°C, no averaging        |     | 1.0       |             | Degrees rms |

| 4                                                        | At 25°C, maximum averaging   |     | 0.1       |             | Degrees rms |

| Noise Density                                            | At 25°C, no averaging        |     | 0.037     |             | Degrees/√Hz |

| FREQUENCY RESPONSE                                       |                              |     |           |             | rms         |

| Sensor Bandwidth                                         |                              |     | 2250      |             | Hz          |

| Sensor Resonant Frequency                                |                              |     | 5.5       |             | kHz         |

| SELF-TEST STATE                                          |                              |     | 3.3       |             | KIIZ        |

| Output Change When Active                                | At 25℃                       |     | 34        |             | Degrees     |

| TEMPERATURE SENSOR                                       | At 23 C                      |     | 34        |             | Degrees     |

| Output at 25°C                                           |                              |     | 1278      |             | LSB         |

| Scale Factor                                             |                              |     | -2.13     |             | LSB/°C      |

| ADC INPUT                                                |                              |     | -2.13     |             | LSB/ C      |

| Resolution                                               |                              |     | 12        |             | Dita        |

|                                                          |                              |     | 12<br>±2  |             | Bits<br>LSB |

| Integral Nonlinearity Differential Nonlinearity          |                              |     |           |             | LSB         |

| Offset Error                                             |                              |     | ±1<br>±4  |             | LSB         |

| Gain Error                                               |                              |     |           |             |             |

|                                                          |                              |     | ±2        | 2.5         | LSB<br>V    |

| Input Range                                              | Domin no a socialei co       | 0   | 20        | 2.5         | -           |

| Input Capacitance ON-CHIP VOLTAGE REFERENCE              | During acquisition           |     | 20        |             | pF<br>V     |

|                                                          | A+ 25%C                      | 10  | 2.5       | . 10        | _ ·         |

| Accuracy                                                 | At 25°C                      | -10 | . 40      | +10         | mV          |

| Reference Temperature Coefficient                        |                              |     | ±40       |             | ppm/°C      |

| Output Impedance DAC OUTPUT                              | 510/100 Ft CND               |     | 70        | <del></del> | Ω           |

|                                                          | 5 kΩ/100 pF to GND           |     | 4.5       |             | 5           |

| Resolution                                               | 5 C   101 C   1005           |     | 12        |             | Bits        |

| Relative Accuracy                                        | For Code 101 to Code 4095    |     | 4         |             | LSB         |

| Differential Nonlinearity                                |                              |     | 1         |             | LSB         |

| Offset Error                                             |                              |     | ±5        |             | mV          |

| Gain Error                                               |                              |     | ±0.5      |             | %           |

| Output Range                                             |                              |     | 0 to 2.5  |             | V           |

| Output Impedance                                         |                              |     | 2         |             | Ω           |

| Output Settling Time  LOGIC INPUTS                       |                              |     | 10        |             | μς          |

| Input High Voltage, V <sub>INH</sub>                     |                              | 2.0 |           |             | V           |

| Input High Voltage, VINL                                 |                              | 2.0 |           | 0.8         | V           |

| Logic 1 Input Current, IINH                              | $V_{IH} = VDD$               |     | ±0.2      | 0.8<br>±1   |             |

| Logic 1 Input Current, IINH  Logic 0 Input Current, IINL |                              |     | ±0.2      |             | μΑ          |

| Input Capacitance, C <sub>IN</sub>                       | $V_{IL} = 0 V$               |     | -40<br>10 | -60         | μA          |

| input Capacitance, Cin                                   |                              |     | 10        |             | pF          |

| Parameter                            | Conditions                                                                | Min    | Тур   | Max | Unit    |

|--------------------------------------|---------------------------------------------------------------------------|--------|-------|-----|---------|

| DIGITAL OUTPUTS                      |                                                                           |        |       |     |         |

| Output High Voltage, V <sub>OH</sub> | Isource = 1.6 mA                                                          | 2.4    |       |     | V       |

| Output Low Voltage, Vol              | $I_{SINK} = 1.6 \text{ mA}$                                               |        |       | 0.4 | V       |

| SLEEP TIMER                          |                                                                           |        |       |     |         |

| Timeout Period <sup>2</sup>          |                                                                           | 0.5    |       | 128 | Seconds |

| FLASH MEMORY                         |                                                                           |        |       |     |         |

| Endurance <sup>3</sup>               |                                                                           | 20,000 |       |     | Cycles  |

| Data Retention <sup>4</sup>          | T <sub>J</sub> = 85°C                                                     | 20     |       |     | Years   |

| CONVERSION RATE                      |                                                                           |        |       |     |         |

| Minimum Conversion Time              |                                                                           |        | 244   |     | μs      |

| Maximum Conversion Time              |                                                                           |        | 484   |     | ms      |

| Maximum Throughput Rate              |                                                                           |        | 4096  |     | SPS     |

| Minimum Throughput Rate              |                                                                           |        | 2.066 |     | SPS     |

| POWER SUPPLY                         |                                                                           |        |       |     |         |

| Operating Voltage Range VDD          |                                                                           | 3.0    | 3.3   | 3.6 | V       |

| Power Supply Current                 | Normal mode, SMPL_TIME $\geq$ 0x08 (f <sub>S</sub> $\leq$ 910 Hz) at 25°C |        | 11    | 14  | mA      |

|                                      | Fast mode, SMPL_TIME $\leq$ 0x07 (f <sub>s</sub> $\geq$ 1024 Hz) at 25°C  |        | 36    | 42  | mA      |

|                                      | Sleep mode at 25°C                                                        |        | 500   | 750 | μΑ      |

| Turn-On Time                         |                                                                           |        | 130   |     | ms      |

This sensor relies on the earth's gravity to provide accurate incline angle measurements. The axis of rotation must be perpendicular to the earth's gravity to maintain the factory-calibrated accuracy of the sensor.

Guaranteed by design.

Endurance is qualified as per JEDEC Standard 22 Method A117 and measured at -40°C, +25°C, +85°C, and +125°C.

Retention lifetime equivalent at junction temperature (TJ) 55°C as per JEDEC Standard 22 Method A117. Retention lifetime decreases with junction temperature.

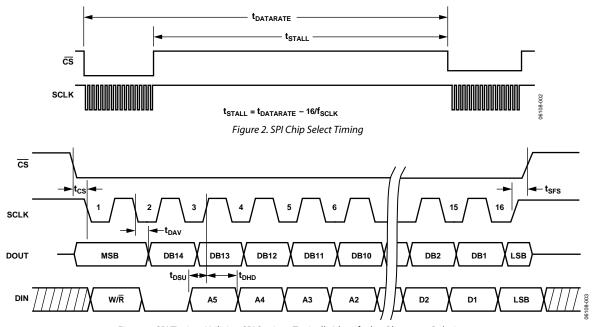

#### **TIMING SPECIFICATIONS**

$T_A = +25$ °C, VDD = 3.3 V, tilt = 0°, unless otherwise noted.

Table 2.

| Parameter             | Description                                                                           | Min <sup>1</sup> | Тур | Max  | Unit |

|-----------------------|---------------------------------------------------------------------------------------|------------------|-----|------|------|

| f <sub>SCLK</sub>     | Fast mode, SMPL_TIME $\leq$ 0x07 ( $f_S \geq$ 1024 Hz)                                | 0.01             |     | 2.5  | MHz  |

|                       | Normal mode, SMPL_TIME $\geq$ 0x08 (f <sub>S</sub> $\leq$ 910 Hz)                     | 0.01             |     | 1.0  | MHz  |

| t <sub>DATARATE</sub> | Chip select period, fast mode, SMPL_TIME $\leq$ 0x07 (f <sub>S</sub> $\geq$ 1024 Hz)  | 40               |     |      | μs   |

|                       | Chip select period, normal mode, SMPL_TIME $\geq$ 0x08 (f <sub>s</sub> $\leq$ 910 Hz) | 100              |     |      | μs   |

| tcs                   | Chip select to clock edge                                                             | 48.8             |     |      | ns   |

| t <sub>DAV</sub>      | Data output valid after SCLK falling edge <sup>2</sup>                                |                  |     | 100  | ns   |

| t <sub>DSU</sub>      | Data input setup time before SCLK rising edge                                         | 24.4             |     |      | ns   |

| t <sub>DHD</sub>      | Data input hold time after SCLK rising edge                                           | 48.8             |     |      | ns   |

| $t_{DF}$              | Data output fall time                                                                 |                  | 5   | 12.5 | ns   |

| $t_{DR}$              | Data output rise time                                                                 |                  | 5   | 12.5 | ns   |

| t <sub>SFS</sub>      | CS high after SCLK edge <sup>3</sup>                                                  | 5                |     |      | ns   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design, not production tested.

#### **TIMING DIAGRAMS**

Figure~3.~SPI~Timing,~Utilizing~SPI~Settings~Typically~Identified~as~Phase=1,~Polarity=1

<sup>&</sup>lt;sup>2</sup> The MSB presents an exception to this parameter. The MSB clocks out on the falling edge of CS. The rest of the DOUT bits are clocked after the falling edge of SCLK and are governed by this specification.

<sup>&</sup>lt;sup>3</sup> This parameter may need to be expanded to allow for proper capture of the LSB. After CS goes high, the DOUT line goes into a high impedance state.

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Table 3.                            |                       |

|-------------------------------------|-----------------------|

| Parameter                           | Rating                |

| Acceleration (Any Axis, Unpowered)  | 3500 g                |

| Acceleration (Any Axis, Powered)    | 3500 <i>g</i>         |

| VDD to COM                          | −0.3 V to +7.0 V      |

| Digital Input/Output Voltage to COM | −0.3 V to +5.5 V      |

| Analog Inputs to COM                | -0.3 V to VDD + 0.3 V |

| Operating Temperature Range         | −40°C to +125°C       |

| Storage Temperature Range           | −65°C to +150°C       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 4. Package Characteristics**

| Package Type | θ <sub>JA</sub> | θ <sub>JC</sub> | Device Weight |

|--------------|-----------------|-----------------|---------------|

| 16-Lead LGA  | 250°C/W         | 25°C/W          | 0.6 g         |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

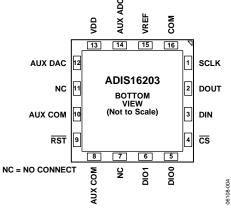

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic   | Type <sup>1</sup> | Description                                                                         |

|---------|------------|-------------------|-------------------------------------------------------------------------------------|

| 1       | SCLK       | I                 | SPI Serial Clock.                                                                   |

| 2       | DOUT       | 0                 | SPI Data Out.                                                                       |

| 3       | DIN        | 1                 | SPI Data In.                                                                        |

| 4       | CS         | 1                 | SPI Chip Select, Active Low. This input frames the serial data transfer.            |

| 5, 6    | DIO0, DIO1 | I/O               | Multifunction Digital I/O Pin.                                                      |

| 7, 11   | NC         | _                 | No Connect.                                                                         |

| 8, 10   | AUX COM    | S                 | Auxiliary Grounds. Connect to GND for proper operation.                             |

| 9       | RST        | 1                 | Reset, Active Low. This input resets the embedded microcontroller to a known state. |

| 12      | AUX DAC    | 0                 | Auxiliary DAC Analog Voltage Output.                                                |

| 13      | VDD        | S                 | +3.3 V Power Supply.                                                                |

| 14      | AUX ADC    | 1                 | Auxiliary ADC Analog Input Voltage.                                                 |

| 15      | VREF       | 0                 | Precision Reference Output.                                                         |

| 16      | COM        | S                 | Common. Reference point for all circuitry in the ADIS16203.                         |

$<sup>^{1}</sup>$  S = supply, O = output, I = input.

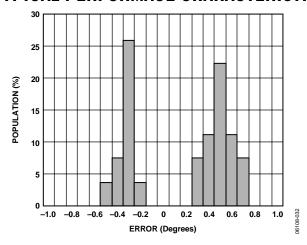

## TYPICAL PERFORMACE CHARACTERISTICS

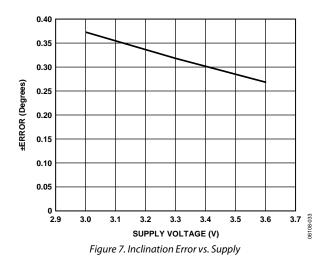

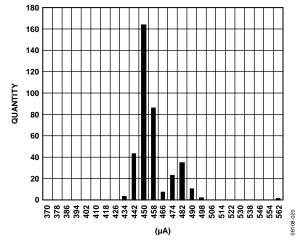

Figure 5. Inclination Error Distribution at  $25^{\circ}$ C/3.3 V, Incline =  $0^{\circ}$

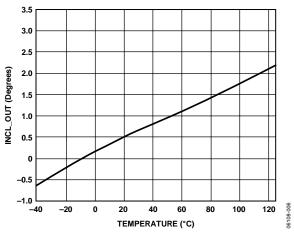

Figure 6. Inclination Error vs. Temperature

70 INCL\_OUT (Degrees) 60 50 40 30 20 10 0 2.9 3.0 3.1 3.2 3.3 3.4 3.5 3.6 3.7 SUPPLY (V)

90

80

Figure 8. Self-Test Shift vs. Supply at 25°C

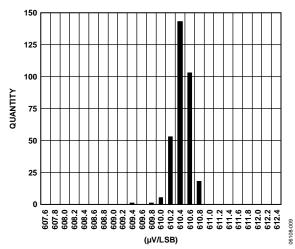

Figure 9. ADC Gain Distribution at 25°C/3.3 V

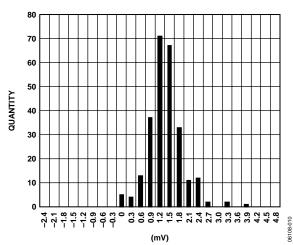

Figure 10. ADC Offset Distribution at 25°C/3.3 V

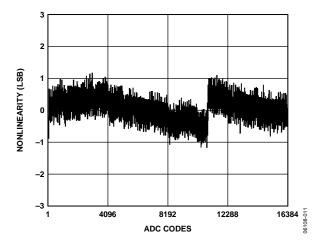

Figure 11. Typical ADC Integral Nonlinearity at 25°C/3.3 V

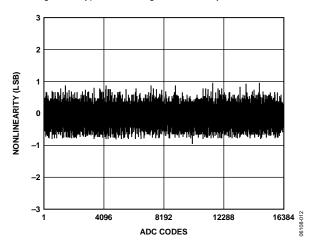

Figure 12. Typical ADC Differential Nonlinearity

Figure 13. DAC Gain Distribution at 25°C/3.3 V

Figure 14. DAC Offset Distribution at 25°C/3.3 V

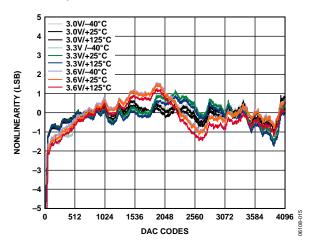

Figure 15. Typical DAC Integral Nonlinearity

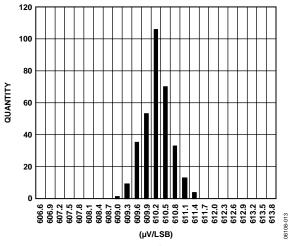

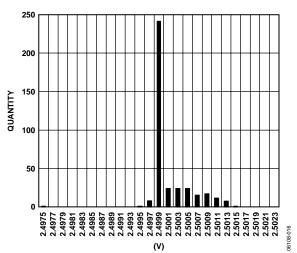

Figure 16. VREF Distribution at 25°C/3.3 V

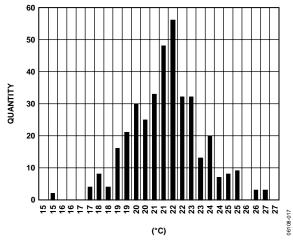

Figure 17. Temperature Distribution at 25°C/3.3 V

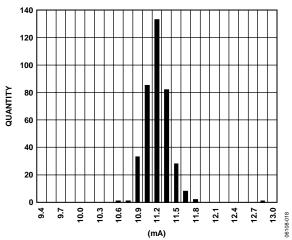

Figure 18. Normal Mode Power Supply Current Distribution at 25°C/3.3 V

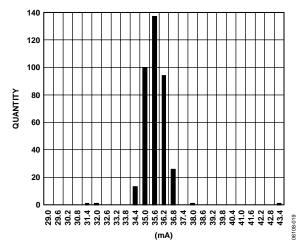

Figure 19. Fast Mode Power Supply Current Distribution at 25°C/3.3 V

Figure 20. Sleep Mode Power Supply Current Distribution at 25°C/3.3 V

Figure 21. Sleep Mode Current vs. Temperature at 3.3 V

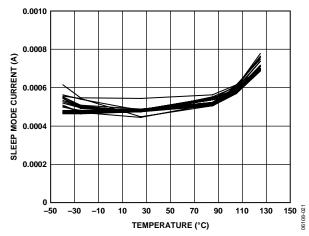

Figure 22. Sleep Mode Current vs. Supply Voltage at 25°C

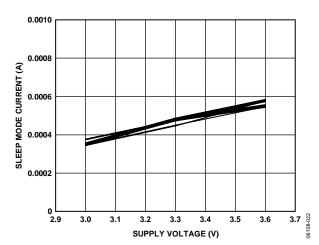

### THEORY OF OPERATION

The ADIS16203 is a calibrated digital inclinometer that provides a full 360° of measurement range in any rotational plane that is parallel to the earth's gravity. A dual-axis accelerometer provides the base-sensing function, which resolves the earth's gravity into two orthogonal vectors, as displayed in Figure 23. A power-efficient approach to a common trigonometric identity converts these orthogonal vectors into an inclineangle measurement.

The digital postprocessing circuit digitizes the sensor outputs and applies sensitivity/offset calibration coefficients prior to angle calculations. A factory calibration produces these coefficients using a full 360° mechanical rotational apparatus. This eliminates the need for system-level calibration in many cases. In addition to calibrating the sensor elements, the ADIS16203 corrects for power-supply-dependent parameters, providing a more robust calibration.

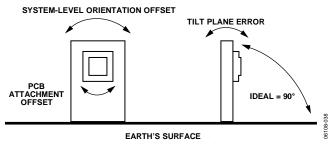

The accuracy of the incline-angle measurements relies on three important factors: the absence of external (aside from gravity) acceleration, managing offset errors introduced during system-level configuration, and maintaining a proper axis of rotation (rotation plane parallel with earth's gravity). All of these factors can influence the acceleration measurements and introduce error. The ADIS16203 provides a simple method for calibrating configuration errors by providing the INCL\_NULL register function. See the Calibration section for more details. In addition, a 10° tilt plane error can introduce as much as  $\pm 1^\circ$  of error in the incline-angle outputs.

Figure 24. ADIS16203 System-Level Orientation

#### **OUTPUT RESPONSE**

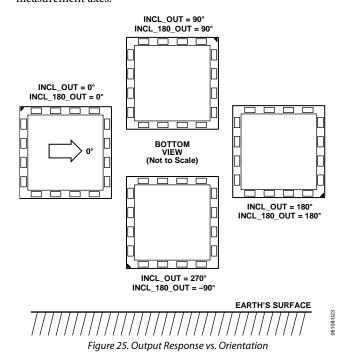

The incline-angle measurements are linear with respect to degrees, and the sensor's orientation produces the output response displayed in Figure 25. This figure is helpful in understanding the basic orientation of the inertial sensor measurement axes.

#### **TEMPERATURE SENSOR**

An internal temperature sensor monitors the accelerometer's junction temperature. The TEMP\_OUT data register provides a digital representation of this measurement. This sensor provides a convenient temperature measurement for system-level characterization and calibration feedback.

### **BASIC OPERATION**

The ADIS16203 is designed for simple integration into industrial system designs, requiring only a 3.3 V power supply and a 4-wire, industry standard SPI. The SPI port facilitates all data transfers with the ADIS16203's registers. Each ADIS16203 function (output data and programming control) has its own register that contains two bytes of data, and each byte of data has its own unique bit map. These two bytes are referred to as *upper* and *lower* bytes, and each has its own 6-bit address.

#### **SERIAL PERIPHERAL INTERFACE (SPI)**

The ADIS16203's SPI port provides a common interface that is supported by a wide variety of digital platforms, including MCUs, DSPs, and FPGAs. Even when a dedicated port is not available, the SPI can be implemented using manual bit manipulation, which is more commonly known as *bit banging*. The purpose of this section is to provide a basic description of SPI operation in the ADIS16203. Please refer to Table 2, Figure 2, and Figure 3 for detailed timing and operation of this port.

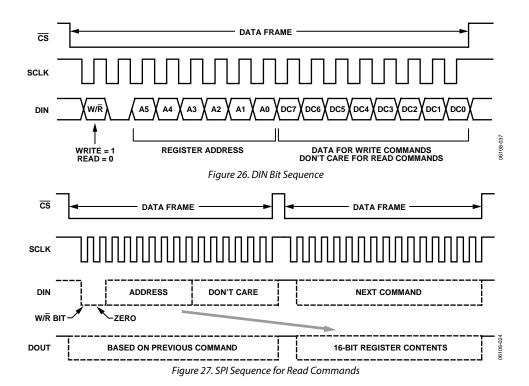

The ADIS16203's SPI port includes four signals: chip select  $(\overline{CS})$ , serial clock (SCLK), data input (DIN), and data output (DOUT). The  $\overline{CS}$  line enables the ADIS16203's SPI port and, in effect, frames each SPI event. When this signal is high, the DOUT lines are in a high impedance state and the signals on DIN and

SCLK have no impact on operation. A complete data frame contains 16 clock cycles. Because the SPI port operates in full duplex mode, it supports simultaneous, 16-bit receive (DIN) and transmit (DOUT) functions during the same data frame.

Figure 26 displays a typical data frame for writing a command to a control register. In this case, the first bit of the DIN sequence is a 1, followed by a 0, then the 6-bit address and 8-bit data command. Because each write command covers a single byte of data, two data frames are required when writing the entire 16-bit space of a register.

Reading the contents of a register requires a modification to the sequence in Figure 26. In this case, the first two bits in the DIN sequence are 0, followed by the address of the register. Each register has two addresses, but either one can be used to access its entire 16 bits of data. The final eight bits of the DIN sequence are irrelevant and can be counted as *don't cares* during a read command. Then, during the next data frame, the DOUT sequence will contain the register's 16-bit data, as shown in Figure 27. Even though a single read command requires two separate data frames, the full duplex mode minimizes this overhead, requiring only one extra data frame when continuously sampling.

#### **DATA OUTPUT REGISTER ACCESS**

The ADIS16203 provides access to two calibrated incline-angle measurements ( $\pm$ 360° and  $\pm$ 180° output formats), power supply measurements, temperature measurements, and an auxiliary 12-bit ADC channel. This output data is continuously updating internally, regardless of user read rates. The follow bit map describes the structure of all output data registers in the ADIS16203.

| В |

|---|

| E |

| ND | EA | D13 | D12 | D11 | D10 | D9 | D8 |

|----|----|-----|-----|-----|-----|----|----|

| D7 | D6 | D5  | D4  | D3  | D2  | D1 | D0 |

The MSB holds the new data (ND) indicator. When the output registers are updated with new data, the ND bit goes to a 1 state. After the output data is read, it returns to a 0 state. The EA bit is used to indicate an alarm condition, which could result from a number of conditions, such as a power supply that is out of the specified operating range. See the Alarms section for more details.

The output data is either 12 or 14 bits in length. For all of the 12-bit output data, the D13 and D12 bits are assigned don't care status.

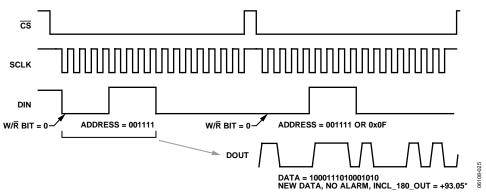

The output data register map is located in Table 6 and provides all of the necessary details for accessing each register's data. Table 7 displays the output coding for the  $\pm 180^{\circ}$  output data register, INCL\_180\_OUT, and Figure 28 displays a timing diagram example for reading this register.

**Table 6. Data Output Register Information**

| Name         | Function                    | Address    | Resolution<br>(Bits) | Data<br>Format  | Scale Factor<br>(per LSB) |

|--------------|-----------------------------|------------|----------------------|-----------------|---------------------------|

| SUPPLY_OUT   | Power supply data           | 0x03, 0x02 | 12                   | Binary          | 1.22 mV                   |

| AUX_ADC      | Auxiliary analog input data | 0x09, 0x08 | 12                   | Binary          | 0.61 mV                   |

| TEMP_OUT     | Sensor temperature data     | 0x0B, 0x0A | 12                   | Binary          | −0.47°C                   |

| INCL_OUT     | Inclination data            | 0x0D, 0x0C | 14                   | Binary          | 0.025°                    |

| INCL_180_OUT | ±180° inclination data      | 0x0F, 0x0E | 14                   | Twos complement | 0.025°                    |

Table 7. Output Coding Example, INCL 180 OUT<sup>1, 2</sup>

| Acceleration Level | Binary Output     | Hex Output | Decimal |  |

|--------------------|-------------------|------------|---------|--|

| +170.10°           | 01 1010 1001 0100 | 0x1A94     | +6804   |  |

| +93.05°            | 00 1110 1000 1010 | 0x0E8A     | +3722   |  |

| +0.625°            | 00 0000 0001 1001 | 0x0019     | +25     |  |

| 0.00°              | 00 0000 0000 0000 | 0x0000     | 0       |  |

| -0.625             | 11 1111 1110 0111 | 0x3FE7     | -25     |  |

| -93.05°            | 11 0001 0111 0110 | 0x3176     | -3722   |  |

| -170.10°           | 11 1100 0001 1000 | 0x256C     | -6804   |  |

$<sup>^{\</sup>mbox{\tiny 1}}$  Two MSBs have been masked off and are not considered in the coding.

<sup>&</sup>lt;sup>2</sup> Nominal sensitivity (0.025°/LSB) and zero offset null performance are assumed.

Figure 28. SPI Sequence Reading INCL\_OUT When Incline Angle = 93.05°

### PROGRAMMING AND CONTROL

#### **CONTROL REGISTER OVERVIEW**

The ADIS16203 offers many programmable features that are controlled by writing commands to the appropriate control registers using the SPI. For added system flexibility and programmability, the following sections describe these controls and specify each register's configuration. A list of features that are available for configuration in this register space follows:

- Calibration: Automatic offset null, manual offset adjustment, factory reset

- Rotational direction: clockwise or counter-clockwise

- Sample rate adjustment

- Filter response optimization

- Alarm settings: threshold or rate of change, and comparison with filtered or unfiltered data

- I/O configuration: data ready, etc.

- Power management: sleep mode, normal and high performance modes

- Auxiliary DAC level setting

- Status checks: verify power supply, SPI communication, package orientation

- Flash™ updates to store configuration

#### CONTROL REGISTER ACCESS

Table 8 displays the control register map for the ADIS16203, including address, volatile status, basic function, and accessibility (read/write). The following sections contain detailed descriptions and configurations for each of these registers.

The ADIS16203 is a Flash-based device with the nonvolatile functional registers implemented as Flash registers. Take into account the endurance limitation of 20,000 writes when considering the system-level integration of these devices. The nonvolatile column in Table 8 indicates the registers that are recovered on power-up. The user must use a manual Flash update command (using the command register) to store the nonvolatile data registers once they are configured properly. When performing a manual Flash update command, the user needs to ensure that the power supply remains within limits for a minimum of 50 ms after the start of the update. This ensures a successful write of the nonvolatile data.

**Table 8. Control Register Mapping**

| Register Name | Туре | Nonvolatile | Address      | Bytes | Function                                                |

|---------------|------|-------------|--------------|-------|---------------------------------------------------------|

|               |      |             | 0x00 to 0x01 | 2     | Reserved                                                |

| INCL_NULL     | R/W  | X           | 0x18         | 2     | Incline null calibration                                |

| ALM_MAG1      | R/W  | Χ           | 0x20         | 2     | Alarm 1 amplitude threshold                             |

| ALM_MAG2      | R/W  | Χ           | 0x22         | 2     | Alarm 2 amplitude threshold                             |

| ALM_SMPL1     | R/W  | Χ           | 0x24         | 2     | Alarm 1 sample period                                   |

| ALM_SMPL2     | R/W  | Χ           | 0x26         | 2     | Alarm 2 sample period                                   |

| ALM_CTRL      | R/W  | Χ           | 0x28         | 2     | Alarm source control register                           |

|               |      |             | 0x2A to 0x2F | 6     | Reserved                                                |

| AUX_DAC       | R/W  |             | 0x30         | 2     | Auxiliary DAC data                                      |

| GPIO_CTRL     | R/W  |             | 0x32         | 2     | Auxiliary digital I/O control register                  |

| MSC_CTRL      | R/W  | X           | 0x34         | 2     | Miscellaneous control register                          |

| SMPL_TIME     | R/W  | Χ           | 0x36         | 2     | ADC sample period control                               |

| AVG_CNT       | R/W  | Χ           | 0x38         | 2     | Defines number of samples used by moving average filter |

| SLP_CNT       | R/W  |             | 0x3A         | 2     | Counter used to determine length of power-down mode     |

| STATUS        | R    |             | 0x3C         | 2     | System status register                                  |

| COMMAND       | W    |             | 0x3E         | 2     | System command register                                 |

### **CONTROL REGISTER DETAILS**

All ADIS16203 control registers are organized into 2-byte segments, and both upper (Bit 8 to Bit 15) and lower (Bit 0 to Bit 7) bytes have unique addresses and can be accessed individually.

MSB LSB

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 |

|-----|-----|-----|-----|-----|-----|----|----|

| D7  | D6  | D5  | D4  | D3  | D2  | D1 | D0 |

This section provides a description of each register, including its purpose, relevant scaling information, bit maps, addresses, and default values.

#### **CALIBRATION**

In addition to the factory calibration, the ADIS16203 provides two user calibration options. Both options utilize the INCL\_NULL control register, which provides an *add* function to the two inclineangle output registers: INCL\_OUT and INCL\_180\_OUT. Because the default contents of INCL\_NULL are 0, adding it to these two outputs has no effect on the output data.

The first calibration option is an automatic null function. This function measures the contents of INCL\_OUT and then writes the inverse of this value into the INCL\_NULL control register. The accuracy of this calibration is dependent on the stability of the INCL\_OUT measurement; therefore, maximizing the filtering will minimize the errors associated with noise. Table 9 displays a sequence that executes the automatic null.

**Table 9. Automatic Null Sequence**

| Step                           | Description                                                      |

|--------------------------------|------------------------------------------------------------------|

| Write 0x08 to Address 0x38     | Sets averaging count to 256 using the AVG_CNT register           |

| Wait for 512 samples           | Waits for the lowest noise data                                  |

| Write 0x01 to Address 0x3E     | Executes the global autonull function using the COMMAND register |

| Restore previous average count |                                                                  |

Increasing the sample rate using the SMPL\_TIME control register will minimize the waiting time if this parameter is critical.

The second option for system-level calibration is manual adjustment. The INCL\_NULL control register can be updated using write commands. Refer to its definition in the INCL\_NULL Register Definition section for details.

The factory calibration can be restored by writing 0x02 to Register Address 0x3E. This restores INCL NULL to 0.

#### **CALIBRATION REGISTER DEFINITION**

**INCL NULL Register Definition**

| Address    | Scale <sup>1</sup> | Default | Format | Access |

|------------|--------------------|---------|--------|--------|

| 0x19, 0x18 | 0.025°             | 0x0000  | Binary | R/W    |

<sup>&</sup>lt;sup>1</sup> Scale is the weight of each LSB.

The INCL\_NULL register is the user controlled register for calibrating system-level inclination offset errors. The maximum calibration range is  $+0^{\circ}$  to  $+359.975^{\circ}$  or 0 to +14,399 decimal codes. The contents of this register are nonvolatile.

Table 10. INCL\_NULL Bit Designations

| Bit   | Description               |

|-------|---------------------------|

| 15:14 | Not necessary, force to 0 |

| 13:0  | Data bits                 |

#### **ALARMS**

The ADIS16203 contains two independent alarm functions that are referred to as Alarm 1 and Alarm 2. The Alarm 1 function is managed by the ALM\_MAG1 and ALM\_SMPL1 control registers. The Alarm 2 function is managed by the ALM\_MAG2 and ALM\_SMPL2 control registers. Both the Alarm 1 and Alarm 2 functions share the ALM\_CTRL register. For simplicity, this section refers to the Alarm 1 functionality only.

The 16-bit ALM\_CTRL register serves several roles in controlling the Alarm 1 function. First, it is used to enable the overall Alarm 1 function and to select the output data variable that is to be monitored for the alarm condition. Second, it is used to select whether the Alarm 1 function is based upon a predefined threshold (THR) level or a predefined rate-of-change (ROC) slope. Third, the ALM\_CTRL register can be used in setting up one of the two general-purpose input/output lines (GPIOs) to serve as a hardware output that indicates when an alarm condition has occurred. Enabling the I/O alarm function as well as setting its polarity and controlling its operation are accomplished using this register. Fourth, this register provides the controls for setting the comparison data as filtered or unfiltered.

Note that when enabled, the hardware output indicator serves both the Alarm 1 and Alarm 2 functions and cannot be used to differentiate between one alarm condition and the other. It is simply used to indicate that an alarm is active and that the user should poll the device via the SPI to determine the source of the alarm condition (see the STATUS Register Definition section).

Because the ALM\_CTRL, MSC\_CTRL, and GPIO\_CTRL control registers can influence the same GPIO pins, a priority level has been established to avoid conflicting assignments of the two GPIO pins. This priority level is defined as MSC\_CTRL, which has precedence over ALM\_CTRL, which has precedence over GPIO\_CTRL.

The ALM\_MAG1 control register used in controlling the Alarm 1 function has two roles. The first role is to store the value with which the output data variable is compared against to discern if an alarm condition exists. The second role is to identify whether the alarm should be active for excursions above or below the alarm limit. If 1 is written to Bit 15 of the ALM\_MAG1 control register, the alarm is active for excursions extending above a given limit. If 0 is written to Bit 15, the alarm is active for excursions dropping below the given limit. The comparison value contained within the ALM\_MAG1 control register is located within the lower 14 bits.

The monitored output register establishes the format of the 14-bit data space in the ALM\_MAG1 and ALM\_MAG2 registers. For example, setting the alarm to monitor INCL\_OUT sets the data format to a 14-bit, twos complement number, which carries a bit weight of 0.025°.

Use caution when monitoring the temperature output register for the alarm conditions. Here, the negative temperature scale factor results in the greater than and less than selections requiring reverse logic.

Setting Bit 11 in the ALM\_CTRL register establishes the mode of operation: threshold or rate of change (ROC). When the ROC function is enabled, the comparison of the output data variable is against the ALM\_MAG1 level averaged over the number of samples as identified in the ALM\_SMPL1 control register. This acts to create a comparison of ( $\Delta$  units/ $\Delta$  time) or the derivative of the output data variable against a predefined slope.

The versatility built into the alarm function allows the user to adapt to several applications. For example, in the case of monitoring twos complement variables, Bit 15 within the ALM\_MAG1 control register can allow for the detection of negative excursions below a fixed level. In addition, the Alarm 1 and Alarm 2 functions can be set to monitor the same variable that allows the user to discern if an output variable remains within a predefined window.

Another potential ROC application is to monitor slowly changing outputs in the inclination level. With the addition of the alarm hardware functionality, the ADIS16203 can be left to run independently of the main processor and interrupt the system only when an alarm condition occurs. Conversely, the alarm condition can be monitored through the routine polling of any one of the seven data output registers.

Bits 4 and 5 in the ALM\_CTRL register establishes whether ALM\_MAG1 and ALM\_MAG2 are compared with filtered or unfiltered data.

ALM\_MAG1 Register Definition

| Address    | Default <sup>1</sup> | Format <sup>2</sup> | Access |

|------------|----------------------|---------------------|--------|

| 0x21, 0x20 | 0x0000               | N/A                 | R/W    |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

The ALM\_MAG1 register contains the threshold level for Alarm 1. The contents of this register are nonvolatile.

Table 11. ALM MAG1 Bit Designations

| Description Greater than Active Alarm Bit. 1: Alarm is active for an output greater than                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                           |

| 1: Alarm is active for an output greater than                                                                                             |

| ALM_MAG1 register setting.                                                                                                                |

| 0: Alarm is active for an output less than ALM_MAG1 register setting.                                                                     |

| Not used.                                                                                                                                 |

| Data Bits. This number can be either twos complement or straight binary. The format is set by the value being monitored by this function. |

| N<br>C                                                                                                                                    |

ALM\_SMPL1 Register Definition

| Address    | Default <sup>1</sup> | Format | Access |

|------------|----------------------|--------|--------|

| 0x25, 0x24 | 0x0000               | Binary | R/W    |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

The ALM\_SMPL1 register contains the sample period information for Alarm 1, when it is set for ROC alarm monitoring. The ROC alarm function averages the change in the output variable over the specified number of samples and compares this change directly to the values specified in the ALM\_MAG1 register. The contents of this register are nonvolatile.

Table 12. ALM SMPL1 Bit Designations

| Bit  | Description |

|------|-------------|

| 15:8 | Not used    |

| 7:0  | Data bits   |

<sup>&</sup>lt;sup>2</sup> Format is established by source of monitored data

**ALM MAG2 Register Definition**

| Address    | Default <sup>1</sup> | Format <sup>2</sup> | Access |

|------------|----------------------|---------------------|--------|

| 0x23, 0x22 | 0x0000               | N/A                 | R/W    |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

The ALM\_MAG2 register contains the threshold level for Alarm 2. The contents of this register are nonvolatile.

Table 13. ALM\_MAG2 Bit Designations

| Bit  | Description                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Greater than Active Alarm Bit.                                                                                                            |

|      | 1: Alarm is active for an output greater than ALM_MAG2 register setting.                                                                  |

|      | 0: Alarm is active for an output less than ALM_MAG2 register setting.                                                                     |

| 14   | Not used.                                                                                                                                 |

| 13:0 | Data Bits. This number can be either twos complement or straight binary. The format is set by the value being monitored by this function. |

ALM\_SMPL2 Register Definition

| Address    | Default <sup>1</sup> | Format | Access |

|------------|----------------------|--------|--------|

| 0x27, 0x26 | 0x0000               | Binary | R/W    |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

The ALM\_SMPL2 register contains the sample period information for Alarm 2, when it is set for ROC alarm monitoring. The ROC alarm function averages the change in the output variable over the specified number of samples and compares this change directly to the values specified in the ALM\_MAG2 register. The contents of this register are nonvolatile.

Table 14. ALM\_SMPL2 Bit Designations

| Bit  | Description |

|------|-------------|

| 15:8 | Not used    |

| 7:0  | Data bits   |

**ALM CTRL Register Definition**

| Address    | Default <sup>1</sup> | Format | Access |

|------------|----------------------|--------|--------|

| 0x29, 0x28 | 0x0000               | N/A    | R/W    |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

The ALM\_CTRL register contains the alarm control variables.

Table 15. ALM CTRL Bit Designations

| Bit   | Value | CTRL Bit Designations  Description                                           |  |  |

|-------|-------|------------------------------------------------------------------------------|--|--|

| 15    |       | Rate of Change (ROC) Enable for Alarm 2                                      |  |  |

|       |       | 1: ROC is active                                                             |  |  |

|       |       | 0: ROC is inactive                                                           |  |  |

| 14:12 |       | Alarm 2 Source Selection                                                     |  |  |

|       | 000   | Alarm disable                                                                |  |  |

|       | 001   | Alarm source: power supply output                                            |  |  |

|       | 010   | Not used                                                                     |  |  |

|       | 011   | Not used                                                                     |  |  |

|       | 100   | Alarm source: auxiliary ADC output                                           |  |  |

|       | 101   | Alarm source: temperature sensor output                                      |  |  |

|       | 110   | Alarm source: INCL_OUT output                                                |  |  |

|       | 111   | Alarm source: INCL_180_OUT output                                            |  |  |

| 11    |       | Rate of Change (ROC) Enable for Alarm 1                                      |  |  |

|       |       | 1: ROC is active                                                             |  |  |

|       |       | 0: ROC is inactive                                                           |  |  |

| 10:8  |       | Alarm 1 Source Selection                                                     |  |  |

|       | 000   | Alarm disable                                                                |  |  |

|       | 001   | Alarm source: power supply output                                            |  |  |

|       | 010   | Not used                                                                     |  |  |

|       | 011   | Not used                                                                     |  |  |

|       | 100   | Alarm source: auxiliary ADC output                                           |  |  |

|       | 101   | Alarm source: temperature sensor output                                      |  |  |

|       | 110   | Alarm source: INCL_OUT output                                                |  |  |

|       | 111   | Alarm source: INCL_180_OUT output                                            |  |  |

| 7:6   |       | Not used                                                                     |  |  |

| 5     |       | ADF2—Alarm Data Filter                                                       |  |  |

|       |       | 1: Use filtered data for comparison                                          |  |  |

|       |       | 0: Use instantaneous data for comparison                                     |  |  |

| 4     |       | ADF1—Alarm Data Filter                                                       |  |  |

|       |       | 1: Use filtered data for comparison 0: Use instantaneous data for comparison |  |  |

| 3     |       | Not used                                                                     |  |  |

| 2     |       | Alarm Output Enable                                                          |  |  |

| 2     |       | 1: Alarm output enabled                                                      |  |  |

|       |       | 0: Alarm output disabled                                                     |  |  |

| 1     |       | Alarm Output Polarity                                                        |  |  |

|       |       | 1: Active high                                                               |  |  |

|       |       | 0: Active low                                                                |  |  |

| 0     |       | Alarm Output Line Select                                                     |  |  |

|       |       | 1: DIO1                                                                      |  |  |

|       |       | 0: DIO0                                                                      |  |  |

<sup>&</sup>lt;sup>2</sup> Format is established by source of monitored data.

#### **SAMPLE PERIOD CONTROL**

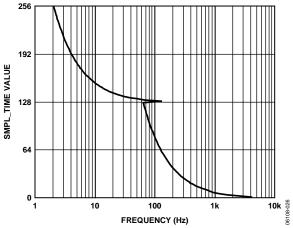

The output data variables within the ADIS16203 are sampled and updated at a rate based upon the SMPL\_TIME control register. The sample period can be precisely controlled over more than a three-decade range using a time base with two settings and a 7-bit binary count. The use of a time base that varies with a ratio of 1:31 allows for a more optimum resolution in the sample period than a straight binary counter. This is reflected in Figure 29, where the frequency is presented on a logarithmic scale.

Note that the sample period given is defined as the cumulative time required to sample, process, and update all data output variables. The data output variables are sampled as a group and in unison with one another. Whatever update rate is selected for one signal, all output data variables are updated at the same rate whether they are monitored via the SPI or not.

For a sample period setting of less than 1098.9  $\mu$ s (SMPL\_TIME  $\leq$  0x07), the overall power dissipation in the part rises by approximately 300%.

Figure 29. SMPL\_TIME Values vs. Sample Frequency

SMPL\_TIME Register Definition

| Address    | Default <sup>1</sup> | Format | Access |

|------------|----------------------|--------|--------|

| 0x37, 0x36 | 0x0008               | N/A    | R/W    |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

The data within this register is nonvolatile, allowing for data recovery upon reset.

Table 16. SMPL\_TIME Bit Descriptions

| Bit  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | Not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7    | ADC Time Base Control. The MSB and TMBS set the time base of the acquisition system to 122.1 $\mu$ s when SR7 = 0 vs. 3.784 ms when SR7 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6:0  | ADC Sample Period Count. The lower seven bits, SP6 to SP0, represent a binary count that results in the combined sample period of the ADC when added to one and then multiplied by the time base. (The combined sample period is the period required to sample and update all seven data outputs.) The minimum setting for the lower seven bits, SP6 to SP0, is 0x01. The overall acquisition time can be varied from 244.2 µs to 15.51 ms in 122.1 µs increments for TMBS = 0 and from 7.57 ms to 481 ms in 3.784 ms increments for TMBS = 1. This equates to the sample rate varying from 4096 SPS to 64.5 SPS for TMBS = 0 and from 132 SPS to 2.08 SPS for TMBS = 1. |

#### FILTERING CONTROL

The ADIS16203 uses two types of filters for the output data. The INCL\_OUT and INCL\_180\_OUT data outputs use a Bartlett Window function, and the SUPPLY\_OUT, AUX\_ADC, and TEMP\_OUT data outputs use a standard moving-averaging filter. The number of taps set by the AVG\_CNT control register establishes the frequency response. The number of taps can be derived from the contents of AVG\_CNT using the following equation:

$$N = 2^{AVG_-CNT}$$

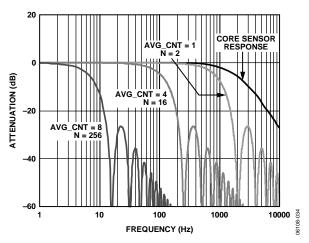

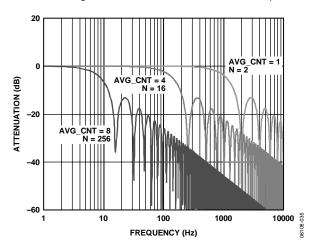

The following equations characterize the expected behavior of each filtering approach. Figure 30 and Figure 31 shows the frequency responses of each filter approach.

Averaging:

$$H_A(f) = \frac{\sin(\pi \times N \times f \times t_s)}{N \times \sin(\pi \times f \times t_s)}$$

Bartlett Window:

$$H_B(f) = H_A^2(f)$$

The primary difference in the frequency responses offered by each approach lies in their side lobes, which are 13 dB better in the Bartlett Windowing approach. The Bartlett Window filtering has two times the latency of the moving average filter.

Figure 30. INCL\_OUT, INCL\_180\_OUT Filter Response

Figure 31. SUPPLY\_OUT, AUX\_ADC, and TEMP\_OUT Filter Response,  $f_S = 4096 \text{ SPS}$

**AVG CNT Register Definition**

| Address    | Default <sup>1</sup> | Format | Access |

|------------|----------------------|--------|--------|

| 0x39, 0x38 | 0x0007               | Binary | R/W    |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

The AVG\_CNT register contains information that represents the number of averages to be applied to the output data. The number of averages can be calculated by powers of 2. The number of averages can be set to 1, 2, 4, 8, 16, 32, 64, 128, or 256.

Table 17. AVG\_CNT Bit Description

| Bit  | Description                                         |

|------|-----------------------------------------------------|

| 15:4 | Not used                                            |

| 3:0  | Data bits (maximum = 1000, or a decimal value of 8) |

#### **POWER-DOWN CONTROL**

The ADIS16203 has the ability to power down for user-defined amounts of time, using the SLP\_CNT control register. The amount of time specified by the SLP\_CNT control register is equal to the binary count of the 8-bit control word multiplied by 0.5 sec. Therefore, the 255 codes cover an overall shutdown period of 127.5 seconds. The SLP\_CNT register is volatile and is set to 0 upon both power-up and subsequent wake-ups from the power-down period. By setting the SLP\_CNT control register to a nonzero state, the ADIS16203 automatically powers down once the next sample period is completed and the data output registers are updated.

Once the ADIS16203 is placed into power-down mode, it can only return to normal operation by timing out, by a reset command (using the RST hardware control line), or by cycling the power applied to the part. Once awake, the data output registers can be scanned to determine what the state of the output registers were prior to powering down. Once the data is recovered, the device can be powered down again by simply writing a nonzero value to the SLP CNT control register and starting the process over.

Once the power-down time is complete, the recovery time for the ADIS16203 is approximately 2 ms. This recovery time is implemented within the device to allow for recovery of the ADC prior to performing the next data conversion. Note that the ND data bit within the data output control registers is cleared when the ADIS16203 is powered down. Likewise, the new data hardware I/O line is placed into an inactive state prior to being powered down. The DAC is placed into a power-down mode as well, resulting in the DAC output dropping to 0 V during the power-down period. All control register settings are retained while powered down with the exception of the SLP\_CNT control register.

#### SLP\_CNT Register Definition

| Address    | Default <sup>1</sup> | Format | Access |

|------------|----------------------|--------|--------|

| 0x3B, 0x3A | 0x0000               | Binary | R/W    |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

Table 18. SLP\_CNT Bit Descriptions

| Bit  | Description |

|------|-------------|

| 15:8 | Not used    |

| 7:0  | Data bits   |

#### **STATUS FEEDBACK**

The status control register within the ADIS16203 is utilized in determining the present state of the device. The ability to monitor the device becomes necessary when and if the ADIS16203 has registered an alarm and/or error condition as indicated by the alarm enable (Bit 14) within the output data registers.

**STATUS Register Definition**

| Address    | Default <sup>1</sup> | Format | Access    |

|------------|----------------------|--------|-----------|

| 0x3D, 0x3C | 0x0000               | N/A    | Read only |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

The STATUS control register contains the alarm/error flags that indicate abnormal operating conditions. See Table 19 for each bit's definition. Bit 0 and Bit 1 will automatically clear when the power supply is in the specified range of operation. Setting Bit 4 in the COMMAND register clears all flags. The flags are set on a continuing basis as long as the error or alarm conditions persist.

**Table 19. STATUS Bit Descriptions**

| Bit   | Description                    |

|-------|--------------------------------|

| 15:10 | Not used                       |

| 9     | Alarm 2 Status                 |

|       | 1: Active                      |

|       | 0: Normal mode                 |

| 8     | Alarm 1 status                 |

|       | 1: Active 0: Normal mode       |

|       |                                |

| 7     | Not used                       |

| 6     | Invalid Orientation            |

|       | 1: Invalid orientation         |

|       | 0: Normal mode                 |

| 5     | Self Test Fail                 |

|       | 1: Self-test failure           |

|       | 0: Self-test pass              |

| 3     | SPI Communications Failure     |

|       | 1: Error condition             |

|       | 0: Normal mode                 |

| 2     | Control Register Update Failed |

|       | 1: Error condition             |

|       | 0: Normal mode.                |

| 1     | Power Supply Above 3.625 V     |

|       | 1: Error condition             |

|       | 0: Normal mode                 |

| 0     | Power Supply Below 2.975 V     |

|       | 1: Error condition             |

|       | l 0: Normal mode               |

#### **COMMAND CONTROL**

The COMMAND control register is utilized in sending global commands to the ADIS16203 device. Any one of the global commands can be implemented by simply writing 1 to its corresponding bit location. The command control register has write-only capability and is volatile. Table 20 describes each of these global commands.

**COMMAND Register Definition**

|            | - <b>J</b>           |        |            |

|------------|----------------------|--------|------------|

| Address    | Default <sup>1</sup> | Format | Access     |

| 0x3F, 0x3E | 0x0000               | N/A    | Write only |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

#### **Table 20. COMMAND Bit Descriptions**

| Bit  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | Not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7    | Software Reset Command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6:5  | Not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4    | Clear Status Register, once per activation                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3    | Manual Flash Update Command. This command is utilized in updating all of the nonvolatile registers to Flash. Once the command is initiated, the supply voltage, VDD, must remain within specified limits for 50 ms to ensure proper update of the nonvolatile registers to Flash.                                                                                                                                                                                                                |

| 2    | Auxiliary DAC Latch Command. This command acts to latch the AUX_DAC control register data into the auxiliary DAC upon receipt of the command. This allows for sequential loading of the upper and lower AUX_DAC data bytes via the SPI without having the auxiliary DAC transition into unwanted, intermediate states based upon the individual AUX_DAC data bytes. Once the two bytes of AUX_DAC are loaded, the DAC latch command is initiated to move the data into the auxiliary DAC itself. |

| 1    | Factory Reset Command. This command allows the user to reset the INCL_NULL register to its nominal setting (0x0000) upon receipt of the command. Data within the moving average filters is reset. As the manual Flash command (COMMAND register, Bit 3), this command stores all of the nonvolatile registers to Flash. Once the command is initiated, the supply voltage, VDD, must remain within specified limits for 50 ms to ensure proper update of the nonvolatile registers to Flash.     |

| 0    | Null Command. This command loads the inclination offset register with a value that zeros out the inclination and outputs. Useful as a single command to simultaneously zero the inclination outputs. As the manual Flash command (COMMAND register, Bit 3), this command stores all of the nonvolatile registers to Flash. Once the command is initiated, the supply voltage, VDD, must remain within specified limits for 50 ms to ensure proper update of the nonvolatile registers to Flash.  |

#### **MISCELLANEOUS CONTROL REGISTER**

The MSC\_CTRL control register governs the operation of several miscellaneous features: using the general purpose I/O for data-ready (DR) hardware I/O function, reversing the polarity of rotation (clockwise vs. counter clockwise), and self-test. The control bits for each of these functions are described in Table 21.

The operation of the data-ready hardware I/O function is very similar to the alarm hardware I/O function (controlled through the ALM\_CTRL control register). In this case, the MSC\_CTRL register can be used in setting up one of the GPIO pins to serve as the hardware output pin that indicates when the sampling, conversion, and processing of the data output variables have been completed. This register provides the ability to enable the data-ready hardware function and establish its polarity.

The data-ready hardware I/O pin is reset automatically to an inactive state part way through the next conversion cycle, resulting in a pulse train with a duty cycle varying from ~15% to 35%, depending upon the sample period setting. Upon completion of the next data processing cycle, the data ready hardware I/O line is set to 1.

The MSC\_CTRL, ALM\_CTRL, and GPIO\_CTRL control registers can influence the same GPIO pins. A priority level has been established to avoid conflicting assignments of the two GPIO pins. This priority level is defined as MSC\_CTRL and has precedence over ALM\_CTRL, which has precedence over GPIO\_CTRL.

The self-test operation exercises the base accelerometer's mechanical structure and establishes a mechanical diagnostic test. The self-test offers the ability to have the ADIS16203 run an internal diagnostic test, which returns a pass/fail condition (see the STATUS register definition of Bit 5 in Table 19). This feature also provides the ability to observe the incline angle outputs during the self-test function, which is nominally 37°, regardless of the incline angle of the device. Note that a self-test changes the contents of SMPL\_TIME to improve the speed of this test. Upon completion, the ADIS16203 restores the original contents to SMPL\_TIME.

#### MSC\_CTRL Register Definition

| Address    | Default <sup>1</sup> | Format | Access |

|------------|----------------------|--------|--------|

| 0x35, 0x34 | 0x0000               | N/A    | R/W    |

<sup>&</sup>lt;sup>1</sup> Default is valid only until the first register write cycle.

The 16-bit miscellaneous control register is used in the controlling of the self-test and data-ready hardware functions. This includes turning on and off the self-test function, as well as configuring the data-ready function. For the data-ready function, the written values are nonvolatile, allowing for data recovery upon reset. The self-test data is volatile and is set to 0s upon reset. This register has read/write capability.

Table 21. MSC\_CTRL Bit Descriptions

| Bit   | Description Descriptions                                                                                                                                                                                       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | Not used                                                                                                                                                                                                       |

| 10    | No Self-Test on Power-Up                                                                                                                                                                                       |

|       | 1: No self-test on power-up or reset 0: Self-test on power-up enabled (typically requires approximately 13 ms in high performance mode and approximately 35 ms in low power mode with every power-up or reset) |

| 9     | Reverse Rotation                                                                                                                                                                                               |

|       | Reverses rotation of both inclination outputs     Normal operation                                                                                                                                             |

| 8     | Self-Test Enable                                                                                                                                                                                               |

|       | 1: ST enabled (continuous self-test) 0: ST disabled                                                                                                                                                            |

| 7:3   | Not used                                                                                                                                                                                                       |

| 2     | Data-Ready Enable                                                                                                                                                                                              |

|       | 1: DR enabled<br>0: DR disabled                                                                                                                                                                                |

| 1     | Data-Ready Polarity                                                                                                                                                                                            |

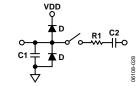

|       | 1: Active high<br>0: Active low                                                                                                                                                                                |