# APPLICATION NOTE

### VACUUM FLUORESCENT DISPLAY MODULE

### CHARACTER DISPLAY MODULE

### M204D08AA

Futaba Vacuum Fluorescent Display Module M204SD08AA, with Futaba VFD 204-SD-008GINK display, produces 20 digits×4rows with 5×8 dot matrix.

Consisting of a VFD, one chip controller, DC-DC converter, the module can be operated by a parallel interface or a synchronous serial interface, and only 5 voltage power source is required to operate the module.

-Futaba Corporation-

# <u>Important Safety Notice</u>

Please read this note carefully before using the product.

#### Warning

- The module should be disconnected from the power supply before handling.

- The power supply should be switched off before connecting or disconnecting the power or interface cables.

- The module contains electronic components that generate high voltages which may cause an electrical shock when touched.

- Do not touch the electronic components of the module with any metal objects.

- The VFD used on the module is made of glass and should be handled with care. When handling the VFD, it is recommended that cotton gloves be used.

- The module is equipped with a circuit protection element.

- Under no circumstances should the module be modified or repaired. Any unauthorized modifications or repairs will invalidate the product warranty.

- The module should be abolished as the factory waste.

| 1. FEATURES ······                                                    | 1  |

|-----------------------------------------------------------------------|----|

| 2. SPECIFICATIONS                                                     |    |

| 2-1. DIMENSIONS, WEIGHT                                               | 1  |

| 2-2. GENERAL SPECIFICATIONS                                           | 1  |

| 2-3. ENVIRONMENTAL SPECIFICATIONS                                     | 2  |

| 2-4. ABSOLUTE MAXIMUM SPECIFICATIONS                                  | 2  |

| 2-5. DC ELECTRICAL SPECIFICATIONS                                     | 2  |

| 2-6. AC ELECTRICAL SPECIFICATIONS                                     | 3  |

| 2-6-1. MOTOROLA M68-TYPE PARALLEL INTERFACE TIMING                    | 3  |

| 2-6-2. INTEL I80-TYPE PARALLEL INTERFACE TIMING                       | 4  |

| 2-6-3. SYNCHRONOUS SERIAL INTERFACE TIMING                            | 6  |

| 2-6-4. RESET TIMING ·····                                             | 7  |

| 3. MODE OF OPERATION                                                  |    |

| 3-1. PARALLEL INTERFACE MODES                                         | 7  |

| 3-1-1. MOTOROLA M68-TYPE MODE                                         | 7  |

| 3-1-2. INTEL I80-TYPE MODE                                            | 8  |

| 3-2. SYNCHRONOUS SERIAL INTERFACE MODE                                | 8  |

| 3-3. RESET MODE                                                       | 9  |

| 4. FUNCTIONAL DESCRIPTION                                             |    |

| 4-1. ADDRESS COUNTER (AC)                                             | 10 |

| 4-2. DISPLAY DATA RAM (DDRAM)                                         | 10 |

| 4-3. CHARACTER GENERATOR RAM (CGRAM)                                  | 11 |

| 4-4. INSTRUCTIONS                                                     | 11 |

| 4-4-1. CLEAR DISPLAY                                                  | 12 |

| 4-4-2. CURSOR HOME                                                    | 12 |

| 4-4-3. ENTRY MODE SET                                                 | 12 |

| 4-4-4. DISPLAY ON/OFF CONTROL                                         | 13 |

| 4-4-5. CURSOR/DISPLAY SHIFT                                           | 13 |

| 4-4-6. FUNCTION SET ·····                                             | 14 |

| 4-4-7. CGRAM ADDRESS SET                                              | 14 |

| 4-4-8. DDRAM ADDRESS SET                                              | 14 |

| 4-4-9. ADDRESS COUNTER READ                                           | 14 |

| 4-4-10. DDRAM OR CGRAM WRITE                                          | 15 |

| 4-4-11. DDRAM OR CGRAM READ                                           | 15 |

| 4-5. RESET CONDITIONS                                                 | 15 |

| 5. CONNECTOR INTERFACE                                                | 16 |

| 6. JUMPER SETTING                                                     | 16 |

| 7. CIRCUIT BLOCK DIAGRAM ·····                                        | 16 |

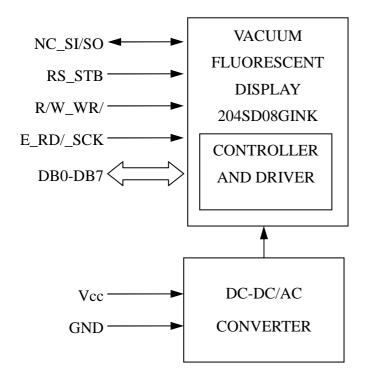

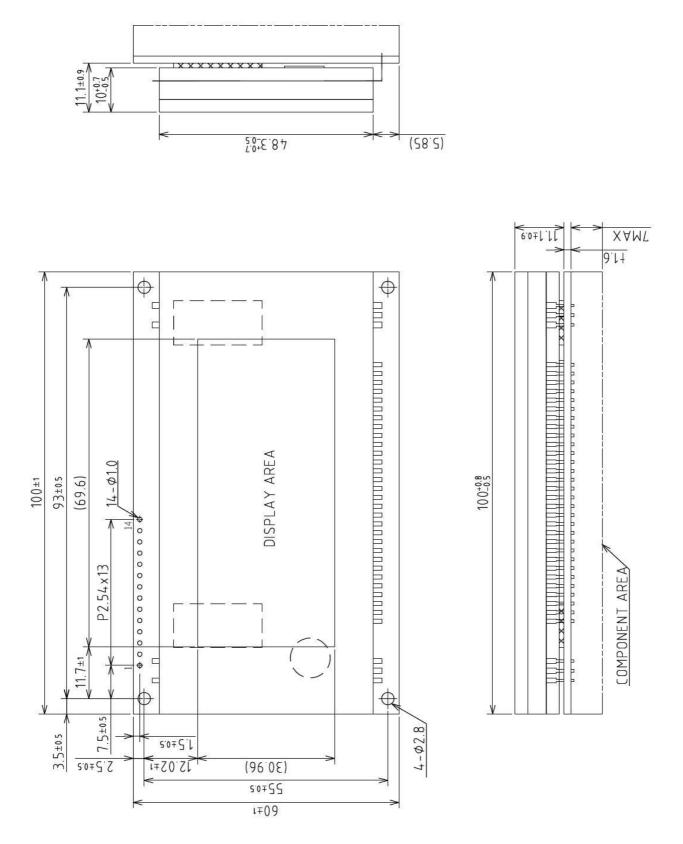

| FIGURE-1 MECHANICAL DRAWING                                           | 17 |

| FIGURE-2 CHARACTER FONT TABLE                                         | 18 |

| 8. WARRANTY                                                           | 19 |

| 9. CAUTIONS FOR DETERMINING AND EXPORTING REGULATED GOODS OR SERVICES | 19 |

| 10. OPERATING RECOMMENDATION                                          | 19 |

Table-2

#### 1. FEATURE

This vacuum fluorescent display (VFD) module consists of a 20 character by 4 line 5×8 dot matrix display, DC-DC converter, and controller/driver circuitry.

The module can be configured for a Motorola M68-type parallel interface, an Intel I80-type parallel interface, or a synchronous serial interface.

When the module is shipped, the parallel (Motorola M68-type) mode is set.

A character generator ROM with 240 5 $\times$ 8 characters is provided along with RAM for the user to program an additional 8 characters. The luminance level of the VFD can be varied by setting two bits in the function set instruction.

Two hundred and forty character fonts consisting of alphabets, numerals and other symbols can be displayed.

This module has a dual-port RAM that allows data and instructions to be the module continuously. Thus, the busy flag is always 0 and the host never has to read the busy flag bit to determine if the module is busy.

Due to this feature, the execution times for each instruction are not specified.

#### 2. SPECIFICATIONS

2-1. DIMENSIONS, WEIGHT (Refer to FIGURE-1)

| ,                   |                                                        | Table-1 |

|---------------------|--------------------------------------------------------|---------|

| Item                | Specification                                          | Unit    |

| Outer<br>Dimensions | (L) $100.0 \pm 1$<br>(W) $60 \pm 1$<br>(T) $20.6$ Max. | mm      |

| Weight              | Approx. 110                                            | g       |

#### 2-2. GENERAL SPECIFICATIONS

|                                    |                                 | 14016-2              |  |  |  |  |

|------------------------------------|---------------------------------|----------------------|--|--|--|--|

| Item                               | Va                              | lue                  |  |  |  |  |

| Number of characters               | 20 characte                     | $ers \times 4$ lines |  |  |  |  |

| Character configuration            | 5×8 do                          | t matrix             |  |  |  |  |

| Character Height                   | 4.844                           | 4 mm                 |  |  |  |  |

| Character Width                    | 2.15                            | mm                   |  |  |  |  |

| Character Pitch                    | 3.55 mm                         |                      |  |  |  |  |

| Line Pitch                         | 8.704 mm                        |                      |  |  |  |  |

| Dot Size                           | $0.35 \times 0$                 | .518 mm              |  |  |  |  |

| Dot Pitch                          | $0.45 \times 0$                 | .618 mm              |  |  |  |  |

| Peak Wavelength of<br>Illumination | Green (λp=505nm) x=0.24, y=0.41 |                      |  |  |  |  |

| Luminance                          | Minimum<br>350 cd/m2            | Typical<br>700 cd/m2 |  |  |  |  |

#### 2-3. ENVIRONMENTAL SPECIFICATIONS

|                       |        |      |      |      | Table-3                                                                                                        |

|-----------------------|--------|------|------|------|----------------------------------------------------------------------------------------------------------------|

| Item                  | Symbol | Min. | Max. | Unit | Comment                                                                                                        |

| Operating Temperature | Topr   | -40  | +85  | °C   |                                                                                                                |

| Storage Temperature   | Tstg   | -55  | +85  | °C   |                                                                                                                |

| Operating Humidity    | Hopr   | 20   | 85   | %RH  | Without condensation                                                                                           |

| Storage Humidity      | Hstg   | 20   | 90   | %RH  | Without condensation                                                                                           |

| Vibration             | _      | _    | 4    | G    | Total amplitude: 1.5mm<br>Freq: 10-55 Hz sine wave<br>Sweep time: 1 min./cycle<br>Duration: 2hrs./axis (X,Y,Z) |

| Shock                 | _      | _    | 40   | G    | Duration: 11ms<br>Wave form: half sine wave<br>3 times/axis (X,Y,Z,-X,-Y,-Z)                                   |

#### 2-4. ABSOLUTE MAXIMUM SPECIFICATIONS

|                      |              | 0110 |                 | Table-4 |

|----------------------|--------------|------|-----------------|---------|

| Item                 | Symbol       | Min. | Max.            | Unit    |

| Supply Voltage       | Vcc          | -0.3 | 6.5             | V       |

| Input signal Voltage | $V_{\rm IN}$ | -0.3 | <i>Vcc</i> +0.3 | V       |

#### 2-5. DC ELECTRICAL SPECIFICATIONS

| 2 5. De Elle Intent Si                                  |                   |                   |                                |      |        | Table-5 |

|---------------------------------------------------------|-------------------|-------------------|--------------------------------|------|--------|---------|

| Item                                                    | Conditions        | Symbol            | Min.                           | Тур. | Max.   | Unit    |

| Supply Voltage                                          |                   | Vcc               | 4.5                            | 5.0  | 5.5    | V       |

| Supply Current                                          |                   | Icc               | _                              | 350  | 470    | mA      |

| Power Consumption                                       |                   | _                 | _                              | 1.75 | 2.35   | W       |

| High - Level Input Voltage1                             | ExceptE,SCK,      | $V_{\mathrm{IH}}$ | $0.7 \mathrm{x} V \mathrm{cc}$ | _    | Vcc    | V       |

| Low - Level Input Voltage1                              | RESET,<br>R,W(WR) | $V_{\mathrm{IL}}$ | 0                              | _    | 0.2Vcc |         |

| High - Level Output Voltage $(I_{OH} = -0.1 \text{mA})$ |                   | V <sub>OH</sub>   | Vcc-0.5                        | _    | Vcc    | V       |

| Low - Level Output Voltage $(I_{OL} = 0.1 \text{mA})$   |                   | V <sub>OL</sub>   | _                              | _    | 0.5    | V       |

| Input Current                                           |                   | $I_{\mathrm{I}}$  | -500                           | _    | 1.0    | μΑ      |

#### 2-6. AC ELECTRICAL SPECIFICATIONS

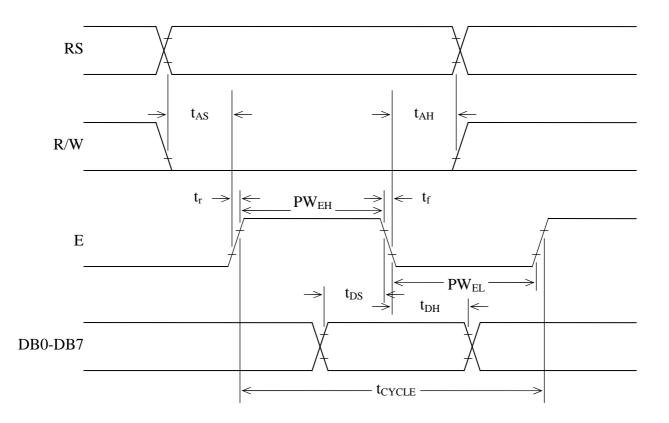

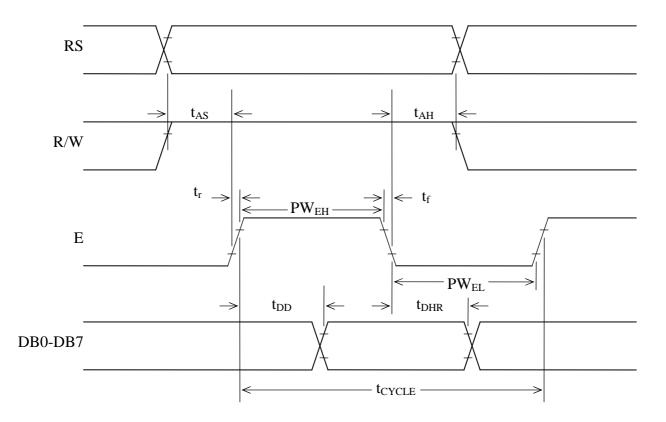

#### 2-6-1. MOTOROLA M68-TYPE PARALLEL INTERFACE TIMING (See Fig. 1 and 2)

| -                       |                    |      |      | Table-6 |

|-------------------------|--------------------|------|------|---------|

| Item                    | Symbol             | Min. | Max. | Unit    |

| RS, R/W Setup Time      | t <sub>AS</sub>    | 20   | _    | ns      |

| RS, R/W Hold Time       | t <sub>AH</sub>    | 10   | _    | ns      |

| Input Signal rise Time  | t <sub>r</sub>     | _    | 15   | ns      |

| Input Signal Fall Time  | t <sub>f</sub>     | _    | 15   | ns      |

| Enable Pulse Width High | PW <sub>EH</sub>   | 230  | _    | ns      |

| Enable Pulse Width Low  | PW <sub>EL</sub>   | 230  | _    | ns      |

| Write Data Setup Time   | t <sub>DS</sub>    | 80   | _    | ns      |

| Write Data Hold Time    | t <sub>DH</sub>    | 10   | _    | ns      |

| Enable Cycle Time       | t <sub>CYCLE</sub> | 500  | _    | ns      |

| Read Data Delay Time    | t <sub>DD</sub>    | _    | 160  | ns      |

| Read Data Hold Time     | t <sub>DHR</sub>   | 5    | _    | ns      |

Note: All timing is specified using 20% and 80% of Vcc as the reference points.

#### Fig. 1. Motorola M68-Type Parallel Interface Write Cycle Timing

Fig. 2. Motorola M68-Type Parallel Interface Read Cycle Timing

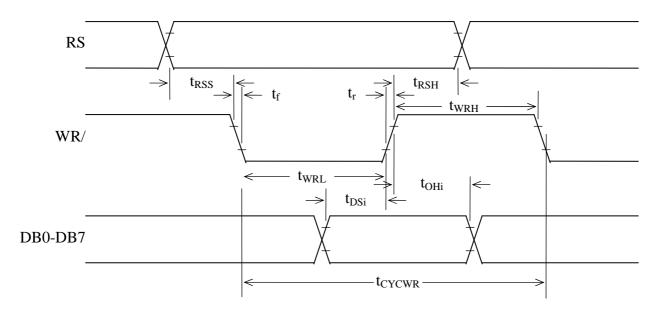

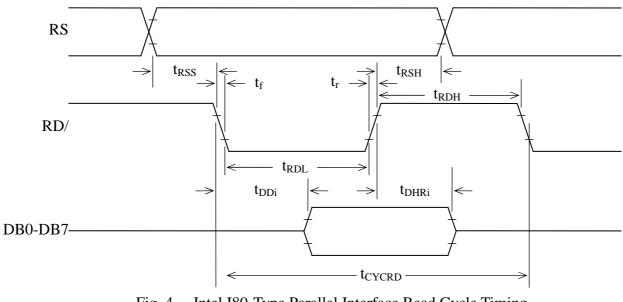

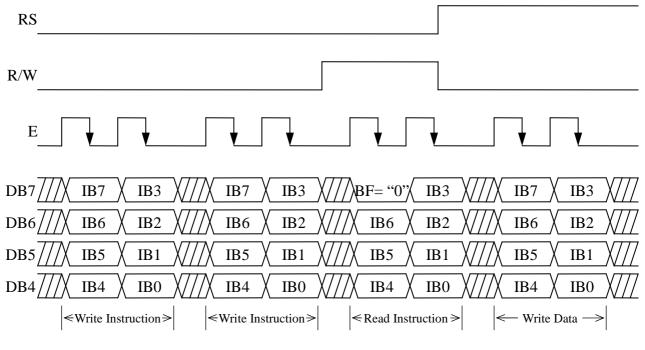

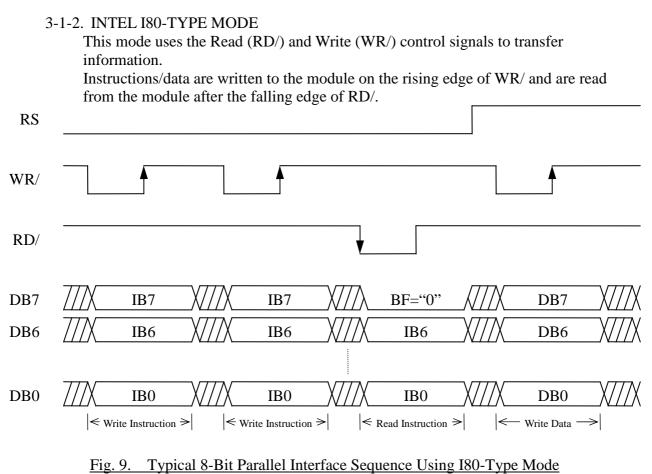

### 2-6-2. INTEL I80-TYPE PARALLEL INTERFACE TIMING (See Fig. 3 and 4)

Table-7 Item Symbol Min. Max. Unit **RS** Setup Time 10 t<sub>RSS</sub> ns \_ **RS** Hold Time 20 \_ ns t<sub>RSH</sub> Input Signal Fall Time 15  $t_{\rm f}$ \_ ns Input Signal Rise Time 15 tr \_ ns WR/ Pulse Width Low 30 \_ t<sub>WRL</sub> ns WR/ Pulse Width High 100 t<sub>WRH</sub> ns \_ Write Data Setup Time 30 t<sub>DSi</sub> \_ ns Write Data Hold Time 10 ns t<sub>DHi</sub> \_ WR/ Cycle Time 166 ns t<sub>CYCWR</sub> \_ **RD/Cycle** Time 166 ns t<sub>CYCRD</sub> — RD/ Pulse Width Low 70 t<sub>RDL</sub> ns \_ RD/ Pulse Width High 100 ns t<sub>RDH</sub> \_ Read Data Delay Time 70 t<sub>DDi</sub> \_ ns Read Data Hold Time 5  $t_{DHRi}$ ns \_

Note: All timing is specified using 20% and 80% of Vcc as the reference points.

Fig. 3. Intel I80-Type Parallel Interface Write Cycle Timing

Fig. 4. Intel I80-Type Parallel Interface Read Cycle Timing

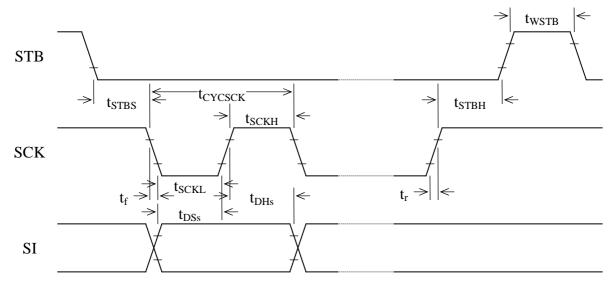

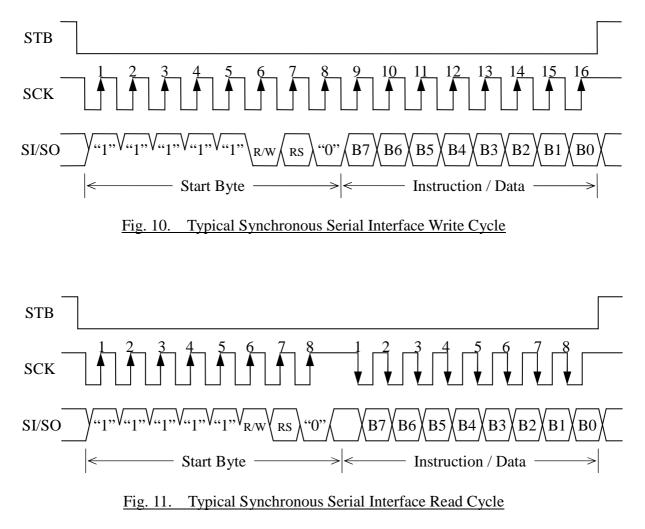

## 2-6-3. SYNCHRONOUS SERIAL INTERFACE TIMING (See Fig. 5, 6, 10, and 11)

|                             |                     |      |      | Table-8 |

|-----------------------------|---------------------|------|------|---------|

| Item                        | Symbol              | Min. | Max. | Unit    |

| STB Setup Time              | t <sub>STBS</sub>   | 100  | _    | ns      |

| STB Hold Time               | t <sub>STBH</sub>   | 500  | _    | ns      |

| Input Signal Fall Time      | t <sub>f</sub>      | _    | 15   | ns      |

| Input Signal Rise Time      | t <sub>r</sub>      | _    | 15   | ns      |

| STB Pulse Width High        | t <sub>WSTB</sub>   | 500  | _    | ns      |

| SCK Pulse Width High        | t <sub>SCKH</sub>   | 200  | _    | ns      |

| SCK Pulse Width Low         | t <sub>SCKL</sub>   | 200  | _    | ns      |

| SI Data Setup Time          | t <sub>DSs</sub>    | 100  | _    | ns      |

| SI Data Hold Time           | t <sub>DHs</sub>    | 100  | _    | ns      |

| SCK Cycle Time              | t <sub>CYCSCK</sub> | 500  | _    | ns      |

| SCK Wait Time Between Bytes | t <sub>WAIT</sub>   | 1    | _    | us      |

| SO Data Delay Time          | t <sub>DDs</sub>    | _    | 150  | ns      |

| SO Data Hold Time           | t <sub>DHRs</sub>   | 5    | _    | ns      |

Note: All timing is specified using 20% and 80% of Vcc as the reference points.

#### Fig. 5. Synchronous Serial Interface Write Cycle Timing

#### Fig. 6. Synchronous Serial Interface Read Cycle Timing

## 2-6-4. RESET TIMING (See Fig. 7)

| 8.17        |                                |                                 |                     |      | Table-9 |

|-------------|--------------------------------|---------------------------------|---------------------|------|---------|

|             | Item                           | Symbol                          | Min.                | Max. | Unit    |

| Delay Time  | for internal reset at power-up | t <sub>RSTD</sub>               | 100                 | _    | ms      |

| Reset Risin | g Time                         | t <sub>R</sub>                  | 1                   | _    | us      |

| Vcc Off Tin | ne                             | t <sub>OFF</sub>                | 1                   |      | us      |

| Vcc         | 0.2V                           | <ul><li>4.5V</li><li></li></ul> | t <sub>RSTD</sub> — | >    |         |

| STB         |                                |                                 |                     |      |         |

Fig. 7. Power-Up Internal Reset Timing

#### 3. MODE OF OPERATION

The following modes of operation are selectable via jumpers (see section 6. jumper Settings).

#### **3-1. PARALLEL INTERFACE MODES**

In the parallel interface mode, 8-bit instructions and data are sent between the host and the module using either 4-bit nibbles or 8-bit bytes. Nibbles are transmitted high nibble first on DB4-DB7 (DB0-DB3 are ignored) whereas bytes are transmitted on DB0-DB7. The Register Select (RS) control signal is used to identify DB0-DB7 as an instruction (low) or data (high).

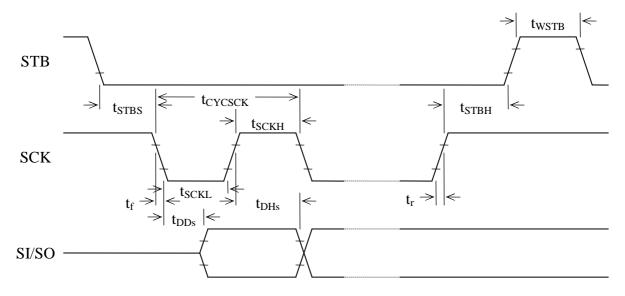

#### 3-1-1. MOTOROLA M68-TYPE MODE

This mode uses the Read/Write (R/W) and Enable (E) control signals to transfer information.

Instructions/data are written to the module on the falling edge of E when R/W is low and are read from the module after the rising edge of E when R/W is high.

#### Fig. 8. Typical 4-Bit Interface Sequence Using M68-Type Mode

#### 3-2. SYNCHRONOUS SERIAL INTERFACE MODE

In the synchronous serial interface mode, instructions and data are sent between the host and the module using 8-bit bytes. Two bytes are required per read/write cycle and are transmitted MSB first. The start byte contains 5 high bits, the Read/Write (R/W) control bit, the Register Select (RS) control bit, and a low bit. The following byte contains the instruction/data bits. The R/W bit determines whether the cycle is a read (high) or a write (low) cycle. The RS bit is used to identify the second byte as an instruction (low) or data (high).

This mode uses the Strobe (STB) control signal, Serial Clock (SCK) input, and Serial I/O (SI/SO) line to transfer information. In a write cycle, bits are clocked into the module on the rising edge of SCK. In a read cycle, bits in the start byte are clocked into the module on the rising edge of SCK. After the minimum wait time, each bit in the instruction/data byte can be read from the module after each falling edge of SCK. Each read/write cycle begins on the falling edge of STB and ends on the rising edge. To be a valid read/write cycle, the STB must go high at the end of the cycle.

#### 3-3. RESET MODE

The module is reset automatically at power-up by internal R-C circuit. However, an external reset mode can also be selected when using one of the parallel interface modes (this option is not available when using the synchronous serial interface mode) which allows the module to be reset by setting the Reset (RST/) input low.

#### 4. FUNCTIONAL DESCRIPTION

#### 4-1. ADDRESS COUNTER (AC)

The AC stores the address of the data being written to and from DDRAM or CGRAM. The AC increments by 1 (overflows from 27H to 40H and from 67H to 00H) or decrements by 1 (underflows from 40H to 27H and from 00H to 67H) after each DDRAM access. The AC increments by 1 (overflows from 3FH to 00H) or decrements by 1 (underflows from 00H to 3FH) after each CGRAM access. When addressing DDRAM, the value in the AC also represents the cursor position.

#### 4-2. DISPLAY DATA RAM (DDRAM)

The DDRAM stores the character code of each character being displayed on the VFD. Valid DDRAM addresses are 00H to 27H and 40H to 67H. DDRAM not being used for display characters can be used as general purpose RAM. The tables below show the relationship between the DDRAM address and the character position on the VFD before and after a display shift (with the number of display lines set to 2).

Relationship before a display shift (non-shifted):

|   | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | <br>32 | 33 | 34 | 35 | 36 | 37 | 37 | 39 | 40 |

|---|----|----|----|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|----|

|   |    |    |    |    |    |    |    |    |    |        |    |    |    |    |    |    |    |    |

| 2 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | <br>5F | 60 | 61 | 62 | 63 | 64 | 65 | 66 | 67 |

#### Relationship after a display shift to the left:

|   | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | <br>32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 |

|---|----|----|----|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|----|

| 1 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | <br>20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 00 |

| 2 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | <br>60 | 61 | 62 | 63 | 64 | 65 | 66 | 67 | 40 |

#### Relationship after a display shift to the right:

|   | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | <br>32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 |

|---|----|----|----|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|----|

| 1 | 27 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | <br>1E | 1F | 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 2 | 67 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | <br>5E | 5F | 60 | 61 | 62 | 63 | 64 | 65 | 66 |

#### 4-3. CHARACTER GENERATOR RAM (CGRAM)

The CGRAM stores the pixel information (1 = pixel on, 0 = pixel off) for the eight user-definable 5×8 characters. Valid CGRAM addresses are 00H to 3FH. CGRAM not being used to define characters can be used as general purpose RAM. Character codes 00H to 07H (or 08H to 0FH) are assigned to the user-definable characters (see section 5.0 Character Font Tables). The table below shows the relationship between the character codes, CGRAM addresses, and CGRAM data for each user-definable character.

|         | С  | 'har | acter  | Co  | de  |    | CC | GRA          | ٩M | [ Ac | ldre | ess |          | C      | CGI | RA | ΜI | Dat | a  |    |       |

|---------|----|------|--------|-----|-----|----|----|--------------|----|------|------|-----|----------|--------|-----|----|----|-----|----|----|-------|

| D7      | D6 | D5   | D4D    | 3D2 | 2D1 | D0 | A5 | A4           | A3 | A2   | A1   | A0  | D7       | 'D61   | D5  | D4 | D3 | D2  | D1 | D0 |       |

| 0       | 0  | 0    | 0 ×    | 0   | 0   | 0  | 0  | 0            | 0  | 0    | 0    | 0   | ×        | ×      | ×   | 1  | 1  | 1   | 1  | 1  |       |

|         |    |      |        |     |     |    |    |              |    | 0    | 0    | 1   |          |        |     | 1  | 0  | 0   | 0  | 0  |       |

|         |    |      |        |     |     |    |    |              |    | 0    | 1    | 0   |          |        |     | 1  | 0  | 0   | 0  | 0  |       |

|         |    |      |        |     |     |    |    |              |    | 0    | 1    | 1   |          |        |     | 1  | 0  | 0   | 0  | 0  | CGRAM |

|         |    |      |        |     |     |    |    |              |    | 1    | 0    | 0   |          |        |     | 1  | 1  | 1   | 1  | 0  | (1)   |

|         |    |      |        |     |     |    |    |              |    | 1    | 0    | 1   |          |        |     | 1  | 0  | 0   | 0  | 0  |       |

|         |    |      | V      |     |     |    |    | ¥            |    | 1    | 1    | 0   |          | V      |     | 1  | 0  | 0   | 0  | 0  |       |

|         |    |      |        |     |     |    |    |              |    | 1    | 1    | 1   |          |        |     | 1  | 0  | 0   | 0  | 0  |       |

| 0       | 0  | 0    | 0 ×    | ; 0 | 0   | 1  | 0  | 0            | 1  | 0    | 0    | 0   | $\times$ | ×      | X   | 0  | 1  | 1   | 1  | 0  |       |

|         |    |      |        |     |     |    |    |              |    | 0    | 0    | 1   |          |        |     | 1  | 0  | 0   | 0  | 1  |       |

|         |    |      |        |     |     |    |    |              |    | 0    | 1    | 0   |          |        |     | 1  | 0  | 0   | 0  | 0  |       |

|         |    |      |        |     |     |    |    |              |    | 0    | 1    | 1   |          |        |     | 1  | 0  | 0   | 0  | 0  | CGRAM |

|         |    |      |        |     |     |    |    |              |    | 1    | 0    | 0   |          |        |     | 1  | 0  | 0   | 0  | 0  | (2)   |

|         |    |      |        |     |     |    |    |              |    | 1    | 0    | 1   |          |        |     | 1  | 0  | 0   | 0  | 0  |       |

|         |    |      | $\vee$ |     |     |    |    | $\mathbf{V}$ |    | 1    | 1    | 0   |          | $\vee$ |     | 1  | 0  | 0   | 0  | 1  |       |

|         |    |      |        |     |     |    |    |              |    | 1    | 1    | 1   |          |        |     | 0  | 1  | 1   | 1  | 0  |       |

| <b></b> |    |      |        |     |     |    |    |              |    |      |      |     |          |        |     |    |    | _   |    |    |       |

| 0       | 0  | 0    | 0 ×    | : 1 | 1   | 1  | 1  | 1            | 1  | 0    | 0    | 0   | ×        | ×      | Х   | 0  | 0  | 1   | 0  | 0  |       |

|         |    |      |        |     |     |    |    |              |    | 0    | 0    | 1   |          |        |     | 0  | 1  | 0   | 1  | 0  |       |

|         |    |      |        |     |     |    |    |              |    | 0    | 1    | 0   |          |        |     | 1  | 0  | 0   | 0  | 1  |       |

|         |    |      |        |     |     |    |    |              |    | 0    | 1    | 1   |          |        |     | 1  | 0  | 0   | 0  | 1  | CGRAM |

|         |    |      |        |     |     |    |    |              |    | 1    | 0    | 0   |          |        |     | 1  | 0  | 0   | 0  | 1  | (8)   |

|         |    |      |        |     |     |    |    |              |    | 1    | 0    | 1   |          |        |     | 1  | 1  | 1   | 1  | 1  |       |

|         |    |      | V      |     |     |    |    | V            |    | 1    | 1    | 0   |          | ¥      |     | 1  | 0  | 0   | 0  | 1  |       |

|         |    |      |        |     |     |    |    |              |    | 1    | 1    | 1   |          |        |     | 1  | 0  | 0   | 0  | 1  |       |

#### 4-4. INSTRUCTIONS

Table-10

| Instruction            | RS | R/W | DB7  | DB6 | DB5         | DB4   | DB3   | DB2     | DB1 | DB0 |

|------------------------|----|-----|------|-----|-------------|-------|-------|---------|-----|-----|

| Clear Display          | 0  | 0   | 0    | 0   | 0           | 0     | 0     | 0       | 0   | 1   |

| Cursor Home            | 0  | 0   | 0    | 0   | 0           | 0     | 0     | 0       | 1   | ×   |

| Entry Mode Set         | 0  | 0   | 0    | 0   | 0           | 0     | 0     | 1       | I/D | S   |

| Display On/Off control | 0  | 0   | 0    | 0   | 0           | 0     | 1     | D       | С   | В   |

| Cursor/Display Shift   | 0  | 0   | 0    | 0   | 0           | 1     | S/C   | R/L     | ×   | ×   |

| Function Set           | 0  | 0   | 0    | 0   | 1           | DL    | Ν     | ×       | BR1 | BR0 |

| CGRAM Address Set      | 0  | 0   | 0    | 1   |             | C     | GRAM  | [ Addre | SS  |     |

| DDRAM Address Set      | 0  | 0   | 1    |     |             | DDR   | AM Ad | ldress  |     |     |

| Address Counter Read   | 0  | 1   | BF=0 |     | AC Contents |       |       |         |     |     |

| DDRAM or CGRAM Write   | 1  | 0   |      |     |             | Write | Data  |         |     |     |

| DDRAM or CGRAM Read    | 1  | 1   |      |     |             | Read  | Data  |         |     |     |

×=don't care

#### 4-4-1. CLEAR DISPLAY

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

This instruction clears the display (without affecting the contents of CGRAM) by performing the following.

- 1) Fills all DDRAM locations with character code 20H (character code for a space).

- 2) Sets the AC to DDRAM address 00H (i.e. sets cursor position to 00H).

- 3) Returns the display to the non-shifted position.

- 4) Sets the I/D bit to 1.

#### 4-4-2. CURSOR HOME

| RS   | R/W    | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 1   | ×   |

| ×=do | n't ca | re  |     |     |     |     |     |     |     |

This instruction returns the cursor to the home position (without affecting the contents of DDRAM or CGRAM) by performing the following.

- 1) Sets the AC to DDRAM address 00H (i.e. sets cursor position to 00H).

- 2) Returns the display to the non-shifted position.

#### 4-4-3. ENTRY MODE SET

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   |

This instruction selects whether the AC (cursor position) increments or decrements after each DDRAM or CGRAM access and determines the direction the information on the display shifts after each DDRAM write. The instruction also enables or disables display shifts after each DDRAM write (information on the display does not shift after a DDRAM read or CGRAM access). DDRAM, CGRAM, and AC contents are not affected by this instruction.

- I/D = 0: The AC decrements after each DDRAM or CGRAM access. If S=1, the information on the display shifts to the right by one character position after each DDRAM write.

- I/D = 1: The AC increments after each DDRAM or CGRAM access. If S=1, the information on the display shifts to the left by one character position after each DDRAM write.

- S = 0: The display shift function is disabled.

- S = 1: The display shift function is enabled.

4-4-4. DISPLAY ON/OFF CONTROL

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | С   | В   |

This instruction selects whether the display and cursor are on or off and selects whether or not the character at the current cursor position blinks. DDRAM, CGRAM, and AC contents are not affected by this instruction.

- D = 0: The display is off (display blank).

- D = 1: The display is on (contents of DDRAM displayed).

- C = 0: The cursor is off.

- C = 1: The cursor is on (8<sup>th</sup> row of pixels).

- B = 0: The blinking character function is disabled.

- B = 1: The blinking character function is enabled (a character with all pixels on will alternate with the character displayed at the current cursor position at about a 1Hz rate with a 50% duty cycle).

#### 4-4-5. CURSOR/DISPLAY SHIFT

| RS   | R/W    | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0      | 0   | 0   | 0   | 1   | S/C | R/L | ×   | ×   |

| ×=do | n't ca | re  |     |     |     |     |     |     |     |

This instruction increments or decrements the AC (cursor position) and shifts the information on the display one character position to the left or right without accessing DDRAM or CGRAM.

DDRAM and CGRAM contents are not affected by this instruction. If the AC was addressing CGRAM prior to this instruction, the AC will be addressing DDRAM after this instruction.

However, if the AC was addressing DDRAM prior this instruction, the AC will still be addressing DDRAM after this instruction.

Table-11

| S/C | R/L | AC Contents (cursor position) | Information on the display                |

|-----|-----|-------------------------------|-------------------------------------------|

| 0   | 0   | Decrements by one             | No change                                 |

| 0   | 1   | Increments by one             | No change                                 |

| 1   | 0   | Decrements by one             | Shifts on character position to the left  |

| 1   | 1   | Increments by one             | Shifts on character position to the right |

| RS   | R/W    | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0      | 0   | 0   | 1   | DL  | Ν   | ×   | BR1 | BR0 |

| ×=dc | n't ca | re  |     |     |     |     |     |     |     |

This instruction sets the width of the data bus for the parallel interface modes, the number of display lines, and the luminance level (brightness) of the VFD. DDRAM, CGRAM, and AC contents are not affected by this instruction.

DL = 0: Sets the data bus width for the parallel interface modes to 4-bit (DB7-DB4). DL = 1: Sets the data bus width for the parallel interface modes to 8-bit (DB7-DB0).

N = 0: Sets the number of display lines to 1.

N = 1: Sets the number of display lines to 2 (It has to be set on this module).

BR1, BR0 = 0,0: Sets the luminance level to 100%.

0,1: Sets the luminance level to 75%.

1,0: Sets the luminance level to 50%.

1,1: Sets the luminance level to 25%.

#### 4-4-7. CGRAM ADDRESS SET

| RS | R/W | DB7 | DB6 | DB5 DB4 DB3 DB2 DB1 DB0 |

|----|-----|-----|-----|-------------------------|

| 0  | 0   | 0   | 1   | CG RAM Address          |

This instruction places the 6-bit CGRAM address specified by DB5-DB0 into the AC (cursor position). Subsequent data writes (reads) will be to (from) CGRAM. DDRAM and CGRAM contents are not affected by this instruction.

#### 4-4-8. DDRAM ADDRESS SET

RS

R/W

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

0

0

1

DD RAM Address

This instruction places the 7-bit DDRAM address specified by DB6-DB0 into the AC (cursor position). Subsequent data writes (reads) will be to (from) DDRAM. DDRAM and CGRAM contents are not affected by this instruction.

#### 4-4-9. ADDRESS COUNTER READ

| RS | R/W | DB7  | DB6 DB5 DB4 DB3 DB2 DB1 DB0 |

|----|-----|------|-----------------------------|

| 0  | 1   | BF=0 | AC Contents                 |

This instruction reads the current 7-bit address from the AC on DB6-DB0 and the busy flag (BF) bit (always 0) on DB7. DDRAM, CGRAM, and AC contents are not affected by this instruction. Because the BF is always 0, the host never has to read the BF bit to determine if the module is busy before sending data or instructions. Therefore, data and instructions can be sent to the module continuously according to the E, WR/, and SCK cycle times specified in section 2.5 AC Timing Specifications. Due to this feature, the execution times for each instruction are not specified.

#### AN-E-2375[14/19]

#### 4-4-10. DDRAM OR CGRAM WRITE

| RS | R/W | DB7 DB6 DB | 5 DB4 DB3  | DB2 | DB1 | DB0 |

|----|-----|------------|------------|-----|-----|-----|

| 1  | 0   |            | Write data |     |     |     |

This instruction writes the 8-bit data byte on DB7-DB0 into the DDRAM or CGRAM location addressed by the AC. The most recent DDRAM or CGRAM Address Set instruction determines whether the write is to DDRAM or CGRAM. This instruction also increments or decrements the AC and shifts the display according to the I/D and S bits set by the Entry Mode Set instruction.

#### 4-4-11. DDRAM OR CGRAM READ

| RS | R/W | DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 |

|----|-----|---------------------------------|

| 1  | 1   | Read data                       |

This instruction reads the 8-bit data byte from the DDRAM or CGRAM location addressed by the AC on DB7-DB0. The most recent DDRAM or CGRAM Address Set instruction determines whether the read is from DDRAM or CGRAM. This instruction also increments or decrements the AC and shifts the display according to the I/D and S bits set by the Entry Mode Set instruction. Before sending this instruction, a DDRAM or CGRAM Address Set instruction should be executed to set the AC to the desired DDRAM or CGRAM address to be read.

#### 4-5. RESET CONDITIONS

After a power-up reset, the module initializes to the following conditions:

- 1) All DDRAM locations are set to 20H (character code for a space).

- 2) The AC is set to DDRAM address 00H (i.e. sets cursor position to 00H).

- 3) The relationship between DDRAM addresses and character positions on the VFD is set to the non-shifted position.

- 4) Entry Mode Set instruction bits:

- I/D = 1: The AC increments after each DDRAM or CGRAM access. If S=1, the information on the display shifts to the left by one character position after each DDRAM write.

- S = 0: The display shift function is disabled.

- 5) Display On/Off Control instruction bits:

- D = 0: The display is off (display blank).

- C = 0: The cursor is off.

- B = 0: The blinking character function is disabled.

- 6) Function Set instruction bits:

- DL = 1: Sets the data bus width for the parallel interface modes to 8-bit (DB7-DB0).

- N = 1: Number of display lines set to 2.

- BR1,BR0=0,0: Sets the luminance level to 100%.

#### 5. CONNECTOR INTERFACE

|     |        |          |            |     |        |          | Table-12   |  |

|-----|--------|----------|------------|-----|--------|----------|------------|--|

| Pin | Serial | Parallel | Parallel   | Pin | Serial | Parallel | Parallel   |  |

| No. | Sella  | (Intel)  | (Motorola) | No. | Seria  | (Intel)  | (Motorola) |  |

| 1   | GND    | GND      | GND        | 2   | Vcc    | Vcc      | Vcc        |  |

| 3   | SI/SO  | NC       | NC         | 4   | STB    | RS       | RS         |  |

| 5   | NC     | WR/      | R/W        | 6   | SCK    | RD/      | Е          |  |

| 7   | NC     | DB0      | DB0        | 8   | NC     | DB1      | DB1        |  |

| 9   | NC     | DB2      | DB2        | 10  | NC     | DB3      | DB3        |  |

| 11  | NC     | DB4      | DB4        | 12  | NC     | DB5      | DB5        |  |

| 13  | NC     | DB6      | DB6        | 14  | NC     | DB7      | DB7        |  |

NC = No Connection

#### 6. JUMPER SETTING

|                     |       |         |       |       | Table-13 |

|---------------------|-------|---------|-------|-------|----------|

| Mode                | J3    | J4      | J5    | J6    | J7       |

| Parallel (Motorola) | open  | short   | open  | short | open     |

| Parallel (Intel)    | open  | shorted | open  | open  | short    |

| Serial              | short | open    | short | short | open     |

Note : JP3~JP7 must be set as shown above for either one of the parallel modes or for the serial mode. When the module is shipped, the parallel (Motorola M68-type) mode is set.

#### 7. CIRCUIT BLOCK DIAGRAM

#### M204SD08AA MECHANICAL DRAWING

#### FIGURE-1

#### M204SD08AA CHARACTER FONT TABLES (English/European Font)

#### FIGURE-2

|      |                   |      | D7<br>D6<br>D5 | 0<br>0<br>0 | 0<br>0      | 0<br>0<br>1 | 0<br>0<br>1 | 0<br>1<br>0 | 0<br>1<br>0 | 0<br>1<br>1 | 0<br>1<br>1 | 1<br>0<br>0 | 1<br>0<br>0 | 1<br>0<br>1 | 1<br>0<br>1 | 1<br>1<br>0 | 1<br>1<br>0 | 1<br>1<br>1 | 1<br>1<br>1 |

|------|-------------------|------|----------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

|      |                   |      | D4             | 0           | 1<br>1<br>1 | 0           | 1           | 0           | 1           | 0           | 1           | 0           | 1           | 0           | 1           | 0<br>0<br>C | 1           | 0<br>E      | 1<br>F      |

| D3 L | D2 D <sup>.</sup> | 1 D0 |                | 0           | <u> </u>    | 2           | 3           | 4           | 5           | 6           | 7           | 8           | 9           | A           | B           |             | D           | •           |             |

| 0    | 0 0               | 0    | 0              |             |             | SP          |             |             |             | ••          | F           |             | $\odot$     |             |             |             |             |             |             |

| 0    | 0 0               | 1    | 1              |             | -           |             |             | Ĥ           |             |             |             |             |             | ·           | •           |             |             |             |             |

| 0    | 01                | 0    | 2              |             | <b>:</b> :: |             |             |             |             |             |             |             | <b>.</b>    | ₫.          |             |             | Ò           | •           |             |

| 0    | 01                | 1    | 3              |             | 33          |             |             |             |             | : <u></u> . | <u></u>     |             | Л           | £.          |             |             | Ó           | <br>        | Ó           |

| 0    | 1 0               | 0    | 4              |             |             | <b>.</b>    | 4           | $\square$   |             |             | ÷.          |             |             | ]=[         |             | Ĥ           | Ô           |             |             |

| 0    | 1 0               | 1    | 5              |             | •           |             |             |             |             |             |             |             |             |             | <b>.</b>    |             |             |             |             |

| 0    | 1 1               | 0    | 6              |             |             |             | 6           |             | Ļ           |             | <b>ن</b> يا | .]]         |             | I           |             |             |             | <b>æ</b>    |             |

| 0    | 1 1               | 1    | 7              |             |             |             |             |             |             |             |             |             | ·¶.         |             | =           |             | 24          | ÷           |             |

| 1    | 0 0               | 0    | 8              |             | •           | ť.          |             | <b>  </b>   | 24          | ŀ           | :::         | <b>!</b>    |             | ÷           | $\odot$     | •<br>•      | ÷           |             |             |

| 1    | 0 0               | 1    | 9              |             | •           |             | ÷           | Ĩ           | ÷           |             | •           |             |             |             | <b>.</b>    |             |             |             |             |

| 1    | 01                | 0    | A              |             |             | :           |             |             |             |             |             | ·           | $\square$   |             |             |             |             |             |             |

| 1    | 01                | 1    | В              |             |             |             | ##<br>;#    | K           |             | k           | Ę           |             | 8           | *           | <u>`</u>    |             |             |             | .*.<br>[]   |

| 1    | 1 0               | 0    | С              |             | :           |             |             |             | •••         |             |             |             | <b></b> :   |             |             |             |             |             |             |

| 1    | 1 0               | 1    | D              |             | •<br>•      |             |             |             |             |             |             |             |             |             |             |             | ÷           |             |             |

| 1    | 1 1               | 0    | Е              |             |             |             |             |             | <b></b>     | <b>P</b> "  |             |             | :           |             |             |             |             |             |             |

| 1    | 1 1               | 1    | F              |             |             |             | ·           |             |             |             |             |             |             |             | ÷           |             |             |             | ••••        |

|      |                   |      |                |             |             |             |             |             |             |             |             |             |             |             |             |             | SP :        | SP          | ACE         |

AN-E-2375[18/19]

#### 8. WARRANTY

This display module is guaranteed for 1 year after a shipment from FUTABA.

# 9. CAUTIONS FOR DETERMINING AND EXPORTING REGULATED GOODS OR SERVICES

This product does not correspond to the goods or services regulated by Japan's Foreign Exchange and Foreign Trade Law. If this product is combined with other products in order to make equipment, whether this product is regulated or not is judged by such newly made equipment. We ask you to determine by yourself whether the equipment corresponds to the regulated goods when this product is incorporated in the equipment.

We also ask you to confirm that this product will not be incorporated in any weapon or used for manufacturing any weapon.

If you export or re-export this product, we recommend you to adopt measures for appropriate export procedures, if any.

#### 10. OPERATING RECOMMENDATION

- 10-1. Since VFD is made of glass material. Avoid applying excessive shock or vibration beyond the specification for the module. Careful handing is essential.

- 10-2. Applying lower voltage than the specified may cause non activation for selected pixels. Conversely, higher voltage may cause may non-selected pixel to be activated. If such a phenomenon is observed, check the voltage level of the power supply.

- 10-3. If the start up time of the supply voltage is slow, the CPU may not be reset. The supply voltage must be risen up to the specified voltage level within 10msec.

- 10-4. DC-DC converter is equipped on the module, the surge current may be approximately 5 times the specified supply current at the power on.

- 10-5. Avoid using the module where excessive noise interference is expected. Noise affects the interface signal and causes improper operation.Keep the length of the interface cable less than 30cm (When the longer cable is required, please contact FUTABA engineering.).

- 10-6. When fixed pattern is displayed for long time, you may see uneven luminance. It is recommended to change the display patterns sometimes in order to keep best display quality.

#### REMARKS

This specification is subject to change without prior in order improve the design and quality. Your consultation with FUTABA sales office is recommended for the use of this module.